一种基于FPGA核系统的智能429-422信号转换模块的设

2.1.1 串行总线控制逻辑设计

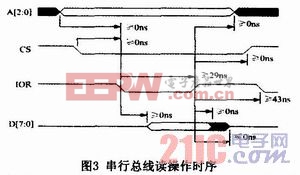

为了将用户自定制的串行总线控制逻辑接入NiosⅡ系统,必须将其挂入Avalon总线。串行总线控制逻辑在设计上必须实现两类端口:一类为Avalon总线端口,Avalon总线时序由NiosⅡ系统实现,用户在逻辑设计时可暂不作考虑;另一类为串行总线控制端口。串行总线读操作时序如图3所示,图中给出了操作时各信号的时序保持关系。

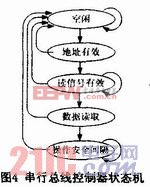

读时序在设计上可以抽象为一个有限状态机,如图4所示。其工作流程为:无数据传输时,状态机停留在空闲状态;若有数据操作请求时,进入“地址有效”的状态;再进入“读信号有效”状态,依次完成“数据读取”、“操作安全间隔”状态(FPGA片外器件要求的两次操作之间的最小间隔)。考虑到异常产生后状态机的稳定性,每个状态都可以在异常产生时返回到默认的“空闲”状态。同时,有些状态作了些等待延时,是为了让控制逻辑与FPGA外部较慢速的器件进行时序匹配。串行总线写操作时序与读操作时序相类似。

2.1.2 429总线控制逻辑设计

429总线控制逻辑设计和串行总线控制逻辑设计方法与上文所述类似,这里不再重复。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码