FPGA与GPS-OEM板的串行通讯系统设计

3.2数据校验和存储设计

要正确读取OEM板的输出语句,首先是判断语句类型,其次是存放数据,然后再确定语句的结束标志。本例中将接收的数据存放在FPGA内部设定的RAM中,而对时间,位置等信息的提取和处理则在其它部分完成。

数据校验模块由FIFO的满信号启动。当检测到满信号有效时。校验模块连续的读取数据并进行处理。当检测到起始标志$后,即进入数据读取和检测。输出数据是以语句的形式出现的,每条语句代表一种数据,每种数据都有它自己的识别码,所以,要根据收到的语句识别码来判断该语句是否为所需要的内容(如GPRMC中,GP为识别符,RMC为语句名)。

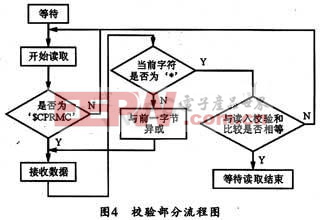

根据NMEA-0183通信标准格式的内容,可对所接收到的数据进行检验。即对接收到的信息逐字节异或。当接收到*时,比较下一字符hh与实际异或值是否相等。若相等,即所接收的数据正确;若不等,则所接收数据无效,系统随之复位存储设备,并等待检测下一组数据。当检测到结束符CR>LF>时,标志数据读取结束,系统向FIFO发出结束标志,并等待下一次数据检测。其系统校验流程图如图4所示。

4 结束语

本文结合PFGA和GPS-25型OEM板的硬件特点,分析了FPGA和OEM板的串行通讯问题,同时重点分析了读取GPS定位信息的设计问题。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码