加强ESD保护的技巧

在本文章中,我们将介绍各种技巧,电路板设计者可以用它们帮助自己实现设计所需的ESD等级,从而保证所选的ESD保护器件能够通过在系统ESD测试。

图1

背景

现代电子设备(从LCD电视到手机)使用的很多芯片集都是采用130nm以下的工艺技术开发而成。这些技术的最低DC电压容差超过3.3V,所以ESD脉冲对这类器件的影响是毁灭性的。并且,“板上”或“片上”ESD保护要求已降至500V,远远低于8kV 现场要求的典型值。

因此,考虑到小型芯片集的弱点,电路板设计者不仅需要外部ESD保护,还需要确保它足够稳定。如先前的白皮书所述,在受保护的数据线路或I/O引脚上安装额定电压为8kV的ESD器件并不能保证在系统测试时芯片集本身会通过8kV的电压。

通常,ESD器件本身不会提供充足的保护,从而导致芯片集过早损坏。本白皮书提供了几点指导意见,设计者可以用它来加强板上ESD保护。

器件布置与布局

器件位置和布局对于让ESD保护器发挥最大效用具有至关重要的作用。为此,设计者最好了解各种寄生电感的板级效应。还特别介绍了电感,因为8kV ESD(即30A)时,仅1nH的电感就会通过关联在PCB迹线上产生30V的尖峰电压。

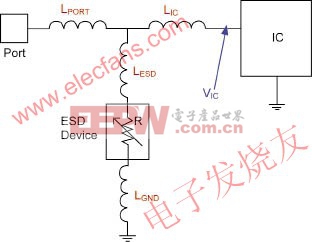

在决定ESD器件布局时,应该考虑4种寄生电感,即LESD、LGND、LIC和LPORT,其位置如图2所示。

图2

LESD和LGND能够提高箝位电压(或VIC),而LIC和LPORT则对设计者有利。我们先介绍这2种有害电感。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码