基于FPGA的PPM系统设计与实现

/*to detect the position of the

shortest pulse*/

module shortest_pulse_det

(clk,ppm_in,dout) ;

input clk,ppm_in;

output dout;

reg dout;

reg temp1,temp2,temp4;

wire temp3;

always @ (posedge clk)

begin

temp1<=ppm_in;

temp2<=temp1;

end

assign temp3=temp2&ppm_in;

always @ (posedge clk)

begin

temp4<=temp3;

dout<=temp4;

end

endmodule

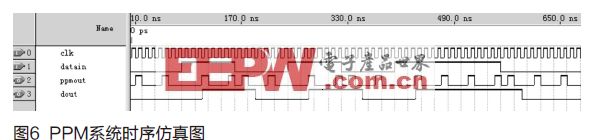

时序仿真

对上述调制与解调模块的顶层原理图互联后,在QuartusII平台下选择了Cyclone系列芯片EP1C3T100C6,运行时序仿真后得到整机系统的时序仿真图如图6所示。

通过图6,可以发现该PPM系统的调制与解调部分均满足要求,有着较好的性能。其中输出比特流(dout)相对于输入比特流(datain)有一定的延迟,这个延迟来源于两个方面,一是系统设计中的整形模块等所引入的延迟,二是布局布线后器件及连线的固有延迟。同时通过查看综合报告,得知整机系统总共使用了14个LE,对逻辑资源的消耗较少。

结语

本文提出的基于FPGA的PPM系统的设计方案,在用简明的Verilog HDL代码实现后,对FPGA的逻辑资源消耗较少,而且电路性能较好,时序仿真结果证明了上述结论。对实际通信中PPM系统的应用具有一定的参考价值。在民用飞机机载设备S模式应答机的应答信号的传输过程中,采用的正是PPM体制,笔者将参考本文的设计方案,并做适当的修改,验证其是否可用于S模式应答机的空地数据链中。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码