理解FPGA中的压稳态及计算压稳态的方法

本白皮书介绍FPGA 中的压稳态,为什么会出现这一现象,它是怎样导致设计失败的。介绍怎样计算压稳态MTBF,重点是对结果造成影响的各种器件和设计参数。

引言

当信号在不相关或者异步时钟域之间传送时,会出现压稳态,它是导致包括FPGA 在内的数字器件系统失败的一种现象。本白皮书介绍FPGA 中的压稳态,解释为什么会出现这一现象,讨论它是怎样导致设计失败的。

通过计算压稳态导致的平均故障间隔时间(MTBF),设计人员知道是否应采取措施来降低这类失败的概率。

本白皮书解释怎样利用各种设计和器件参数来计算MTBF, FPGA 供应商和设计人员怎样提高MTBF。可以通过设计方法和优化措施来降低出现压稳态失败的概率,从而提高系统可靠性。

什么是压稳态?

FPGA 等数字器件中的所有寄存器都有确定的信号时序要求,使每一个寄存器能够正确的采集输入数据,产生输出信号。为保证能够可靠的工作,寄存器输入必须在时钟沿之前稳定一段时间( 寄存器建立时间,即tSU),在时钟沿之后也要保持稳定一段时间( 寄存器保持时间,即tH)。一定的时钟至输出延时 (tCO) 之后,寄存器输出有效。如果信号转换不能满足寄存器的tSU 或者tH 要求,寄存器输出就有可能进入压稳态。在压稳态中,寄存器输出在高电平和低电平状态之间徘徊一段时间,这意味着,输出延时超出设定的tCO 之后才能转换到确定的高电平或者低电平状态。

在同步系统中,输入信号必须满足寄存器时序要求,因此,不会出现压稳态。信号在不相关或者异步时钟域电路之间传输时,一般会出现压稳态问题。在这种情况下,由于信号可能在相对于目的时钟的任意时间到达,因此,设计人员不能保证信号能够满足tSU 和tH 要求。然而,并不是所有不能满足寄存器tSU 或者tH的信号转换都导致压稳态输出。寄存器是否会进入压稳态以及返回稳定状态所需要的时间与器件制造工艺以及实际工作条件有关。在大部分情况下,寄存器会很快返回稳定状态。

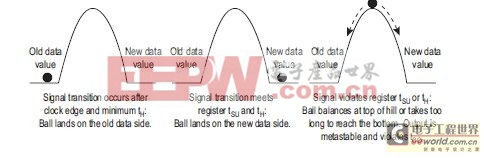

可以把寄存器在时钟边沿采样数据信号形象的看成是球从山上滚落下来,如图1 所示。山的两边代表稳定状态——信号转换之后,信号的老数据和新数据,山顶代表压稳态。如果球从山顶滚落,它会处于不确定状态,实际中,它稍偏向一侧,然后,落到山下。从山顶开始,越到山脚,球到达底部稳定状态的速度越快。

图 1. 利用球从山上落下描述压稳态

如果数据信号在时钟沿之后以最小的 tH 转换,这就类似球从山的“老数据值”一侧落下,输出信号保持在该时钟转换的最初值不变。当寄存器数据输入在时钟沿之前以最小 tSU 转换,保持时间大于最小 tH,这就类似球从山的“新数据值”一侧落下,输出信号很快达到稳定的新状态,满足确定的tCO 时间要求。但是,当寄存器数据输入不能满足tSU 或者 tH, 时,这就类似于球从山顶落下。如果球落在山顶附近,那么,它会花很长时间才能落到山脚,增加了时钟转换到稳定输出的延时,超出了要求的tCO。

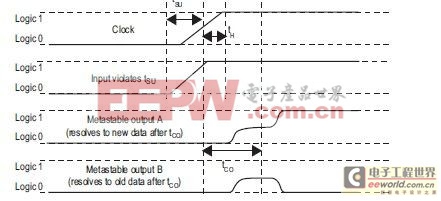

图2 描述了压稳态信号。时钟信号转换时,输入信号从低电平状态转换到高电平状态,不能满足寄存器的tSU 要求。数据输出信号从低电平状态开始,进入压稳态,在高电平和低电平状态之间徘徊。信号输出A 转换到输入数据的新逻辑1 状态,输出B 返回到数据输入最初的逻辑0 状态。在这两种情况下,输出转换到确定的1 或者0 状态的时间被延迟了,超出了寄存器要求的tCO。

图 2. 压稳态输出信号实例

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码