逻辑电平测量器电路原理

作者:dolphin

时间:2012-07-26

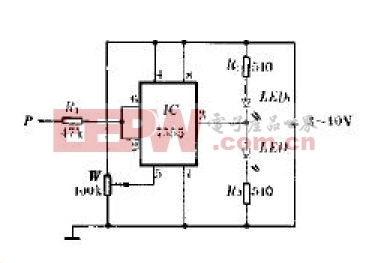

该电路可用来检测电平变化频率不太高的逻辑电平,对于TTL电平、CMOS电平均可检测。

电路如图所示,7555用作滞后电平比较器。当探头P接触高电平时,7555输出低电平使LED1亮、LED2暗。当P接触低电平时,7555输出高电平使LED1不亮,LED2亮。

用来测TTL电平时,电源可采用4.5V电池供电,调W使7555第5脚电压为2.4V.这时2.4V以上为高电平,1.2V以下为低电平。

用于测量CMOS电平时,电源电压需与被测逻辑电路电源电压相近,W中心头断开不用。这时高于电源电压三分之二为高电平,低于电源电压三分之一为低电平。

在测量时还会遇到眼睛来不及观察判断逻辑电平高低的情形,这可根据LED1与LED2不同的发光强度来估计脉冲占空比是大于50%还是小于50%.占空比是大于50%则LED1较亮,反之则LED2较亮。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码