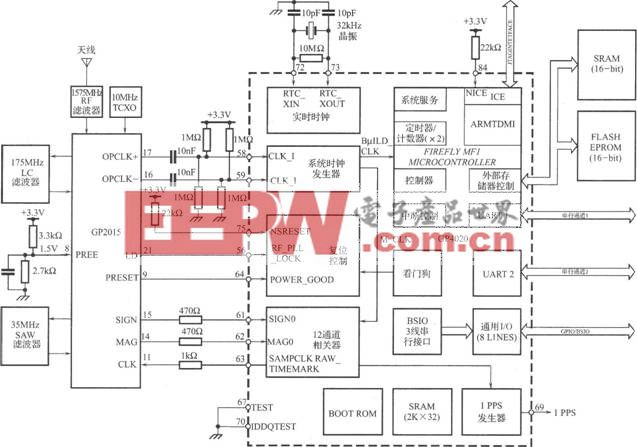

基于GP4020的GPS接收机基带处理器电路

作者:dolphin

时间:2009-07-06

![]() GP4020

GP4020

GP4020是一个完整的GPS接收机数字基带处理器,它结合了GP2021的12通道相关器功能和先进的ARM7TDMI(Thumb)微处理器,达到了较高的集成度水平,减少了GPS接收机系统成本,降低了功耗,增加了功能。GP4020的相关器部分包含有12个相同的跟踪功能模块,每个通道包含对于捕获和跟踪必需的所有元器件,以及其他功能模块。如果不需要12通道,单个通道可以不激活,以降低功耗和处理器的负载。GP4020的微处理器部分包括Firefly MFI微控制器核,Firefly MFl微控制器核包括 ARM7TDMI、Thumb指令、Firefly BμILD模块、JTAG ICEBreakerTM调试接口、UART、BμILD串行 I/O、通用I/O和看门狗功能。GP4020具有:可配置的外部数据总线;工作电源电压3.3V;具有低功耗模式;1PPS UTC输出;3线式BμLD串行输入/输出(BSIO)接口;8个通用输入/输出(GPIO)接口;引导ROM允许通过UART上载软件;8KB内部SRAM;采用PQVP-lOO封装;工作温度范围-40℃~ 85℃。GP4020可以与GP2015和GP2010 C/A码射频下变频器直接连接,构成GPS导航系统、GPS测量接收机等系统。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码