基于AXIe 中 PCIe 高带宽的高速图形传输系统

摘要:E-Beam(电子束)微影技术(Lithography)是下一世代无光罩(maskless)半导体制程。通过无光罩微影技术可使微影制程突破目前20奈米或更小制程的限制。E-Beam 微影系统需要使用极高带宽的数据传输系统,将大量集成电路图案数据,从数据服务器先通过数据传输系统解压缩后,再通过数千条光纤并行传输至 E-Beam 机台,且通道对通道间的时钟偏移(skew)不得大于 2ns。基于高通道高密度及高数据传输带宽的需求,凌华科技采用AXIe平台架构来建置E-Beam 数据传输系统。本文说明如何充分发挥 AXIe平台的特点,来达成此数千通道同步的严格要求。

简介

如上所述,E-Beam 无光罩式微影技术可突破传统光罩式微影技术的限制。概念上就像一台超高速的打印机。不同于打印机喷出墨水,E-Beam机台的电子枪投射出数千组平行电子束,打印至覆盖有光阻剂的晶圆表面,超过 8,000组电子束会通过 MEMS 数组来控制个别电子束的开关,而每个电子束开关的控制命令,则是通过个别的高速光纤输出通道来做控制,因此会需要超过8,000个光纤输出通道。为避免控制命令不同步造成电路图案失真及错误,系统整体需求为所有光纤通道间数据的时钟偏移不能超过 2ns。

可符合经济效益的产出标准为每小时 10片以上,换句话说每6分钟要完成一片晶圆。每一个集成电路光罩档案的数据量可高达 2.5TB,所以另一个挑战是如何实时的将大量数据通过图形传输系统,再通过8,000组以上光纤通道平行输出到E-Beam机台。此数据经系统处理后,可用于控制 E-Beam 系统上的电子束控制数组。为满足这些需求,凌华科技采用基于AXIe系统的FPGA架构解决方案进行数据处理及储存。

AXIe的优点

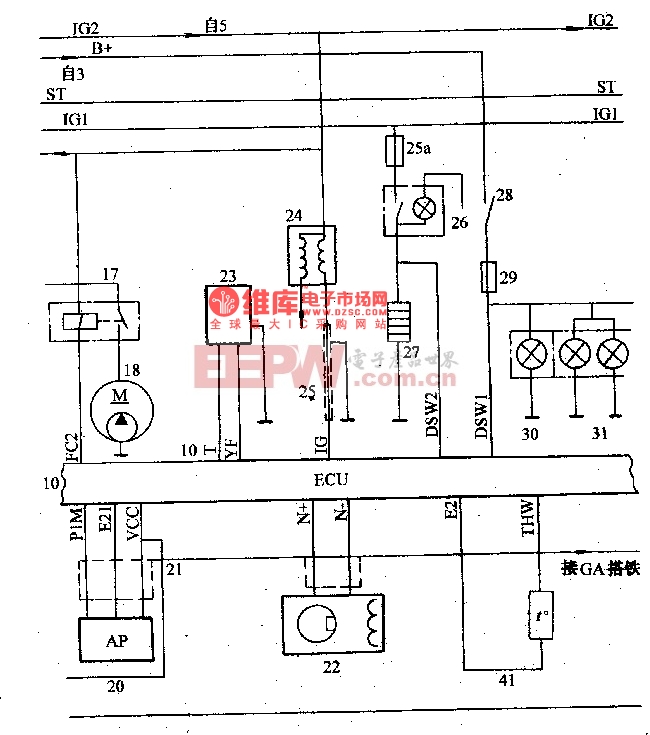

AXIe是基于AdvancedTCA○R(先进电信运算平台)开放式标准所衍生而来,针对高阶量测仪器应用新制定的标准。基于AXIe所具备的以下特点,此图形传输同步系统因此选定AXIe作为该系统的解决方案:

• 6U大尺寸板卡面积,提供足够的空间容纳高密度光纤输出通道电路。

• 每槽可提供高达200瓦高功率的电源供应。

• 有高性能冷却系统,足以解决高功耗所带来的热能。

• 高速PCIe (PCI Express) 总线架构

• 高扩展弹性,单一AXIe机箱可容纳1到14个插槽,而多组机箱可组成一套大量通道数的同步系统。

• 硬件平台管理功能,包括机箱管理控制器、智能型平台管理控制器以及热插入的能力。

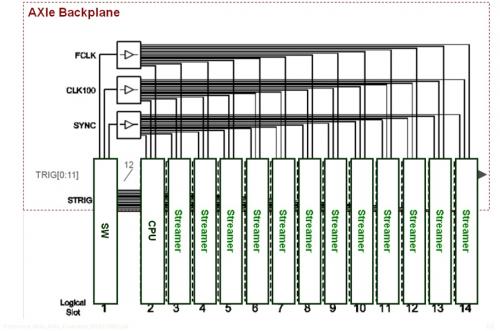

• 同步化(synchronization)及本地总线(local bus)功能可提供各槽所需的精确频率。

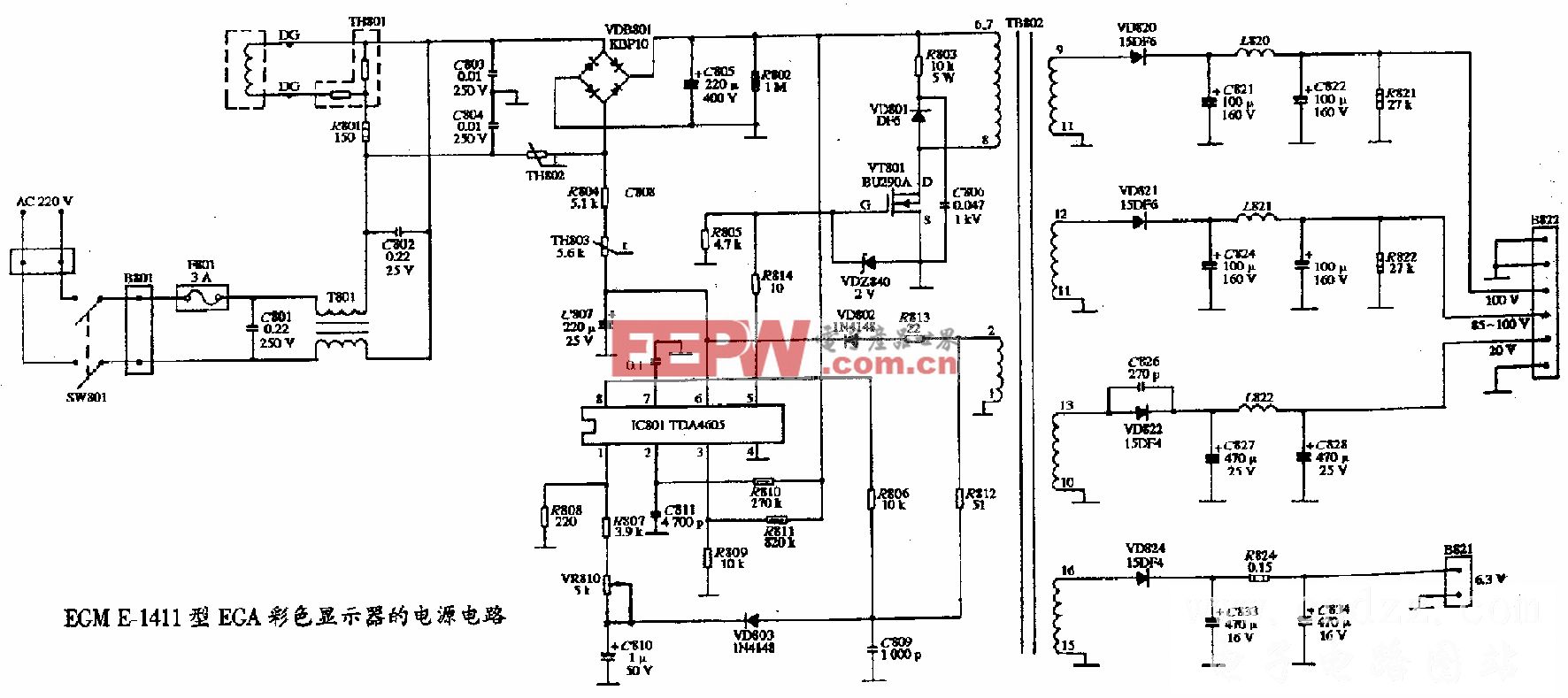

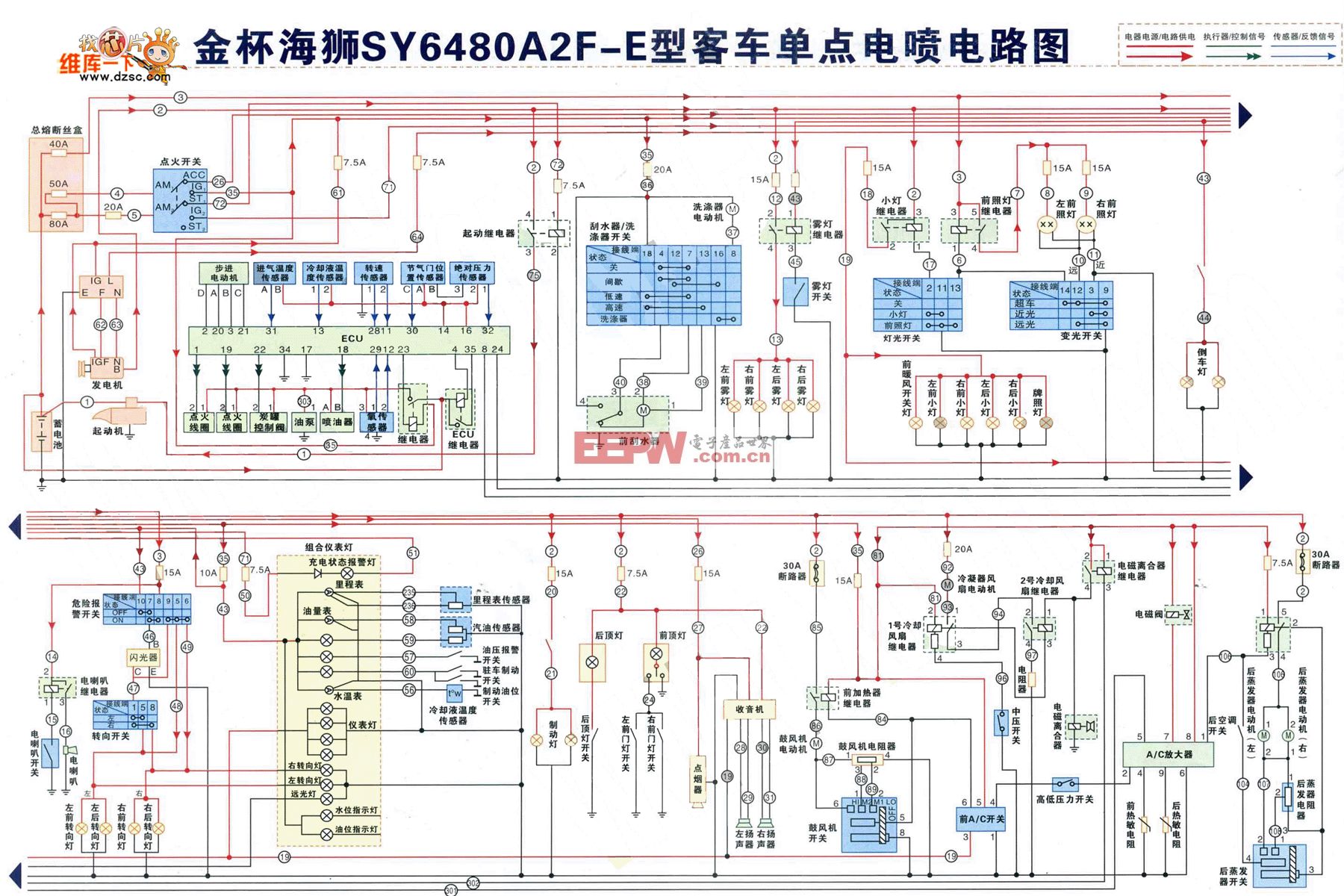

图 1:AXIe 总线分配

图形传输架构

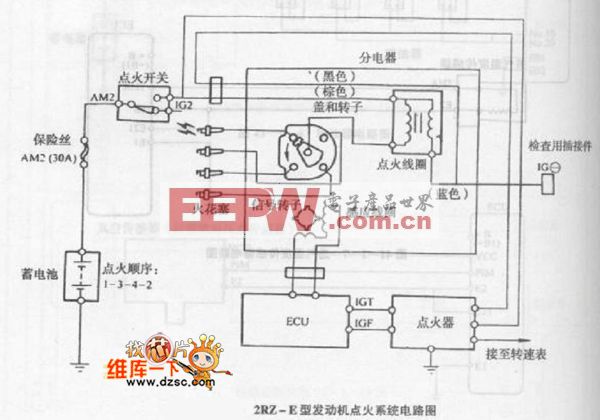

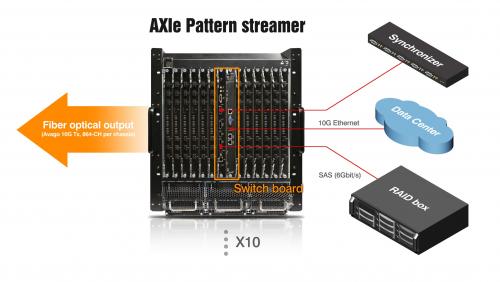

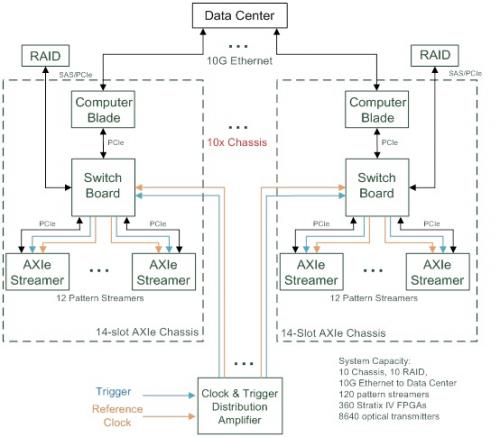

图形传输系统包括计算机模块、PCIe 转换器模块、多组数据传输模块、14槽 AXIe 机箱、外接同步信号产生器以及磁盘阵列(RAID)系统,如图2所示。

在电子束打印期间,计算机模块通过 6 Gbps 的SAS接口,自数据中心(也就是磁盘阵列系统)实时的存取集成电路图文件至系统上的内存储存。PCIe切换器模块位于分享器插槽(hub slot),提供PCIe 通道自动切换功能,负责将储存于内存的集成电路图文件,通过PCIe高速数据接口传输至不同的数据传输模块。每个传输模块均可支持 72 组光纤输出通道。外部同步信号产生器则产生一组共同工作频率及触发信号来让多个机箱可同步运作。

AXIe 大部分独特的功能都被图形传输系统所采用,包括:机构设计及组装、硬件平台管理及监控机制、电源分配机制、主动散热系统以及数据传输接口。

E-Beam系统机箱内为较为复杂的同步化,须利用 AXIe STRIG 及 SYNC 信号,如此可确保点触发系统达成规定的各槽极精确与低抖动的同步化。

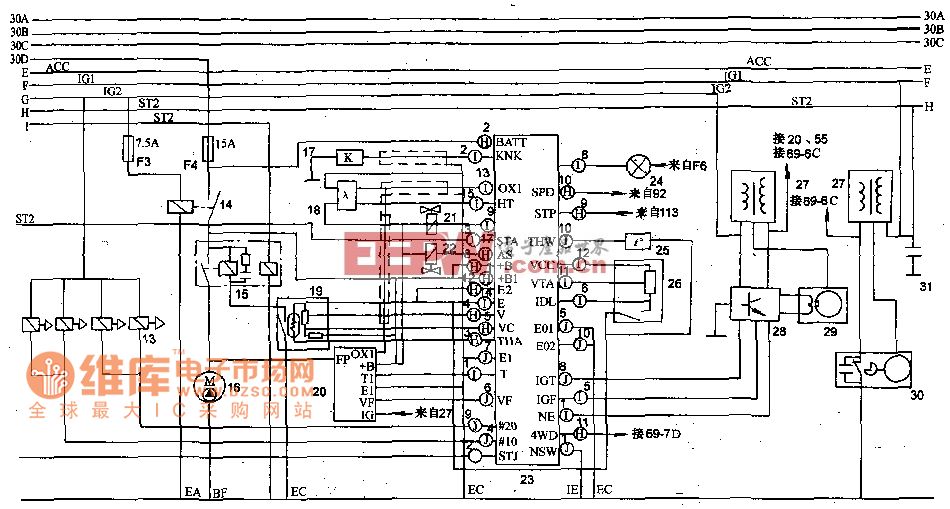

通道间时钟偏移 (Channel-to-channel skew)

E-Beam 系统的硬件设计可确保通道间的时钟偏移最大不超过 2ns。自外部同步信号产生器开始,低偏移扇形输出缓冲器(fan-out buffer)即用于外部同步信号产生器之中,做为将工作频率及同步信号分配到各机箱切换模块的用途。另外,切换模块除提供 PCIe总线自动切换功能外,也负责切换 STRIG、SYNC及相关频率信号,将这些同步信号分配到各插槽上的数据传输模块。在数据传输模块方面,除特别注意各频率及数据信号在PCB上布线都须使用相等路径长度外,在电路输出部分也都采用低偏移缓冲器。最后处理过的数据会由Avago 平行光纤发射器 (AFB-810BHZ-TX) 输出。综合考虑 FPGA 内部绕线及制程、光纤、连接器及 PCB 路径等因素后,计算所得的总体通道间时钟偏移可小于 1ns 以下。

图 2:传输系统架构

图 3:单一 AXIe 机箱满载 12 组传输器模块

图 4:系统频率图

高带宽图形传输

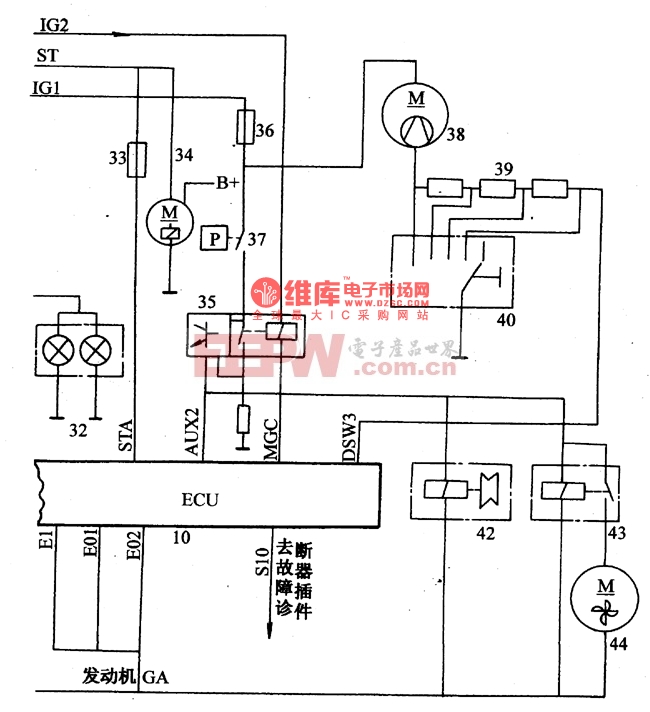

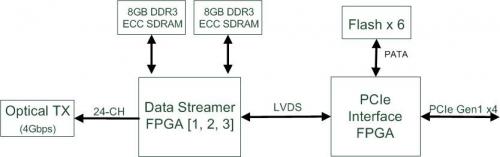

除了跨 10 个机箱下严格的通道间歪斜的要求之外,系统还要求能够实时传输大量数据到光纤输出通道。各图形传输模块配备四组高性能的 FPGA;一颗负责PCIe驱动接口,另外三颗各负责 24 个光纤通道的驱动接口,即单一数据传输模块可提供 72 个光纤输出通道。

集成电路图案数据先自 RAID 磁盘阵列读出后加载主板刀锋服务器的内存,再经由PCIe 总线做直接内存存取(DMA, direct memory access)传输到个别的数据传输模块。数据传输模块上的 PCIe FPGA 接收 DMA 数据并存入模块上的闪存,然后再传输到各图形传输 FPGA 对应的 DDR3 内存储存。图形传输 FPGA 内建有客户自定的解压缩算法,解压缩后的数据会通过光学发射器做同步数据输出。示意图请参见图 5:

图 5:数据传输方块图

其中DDR3 内存切割为两个区块,以便实现「乒乓(ping-pong)」技术,也就是可让大量数据同时间进出内存以优化读/写带宽。各光纤输出通道的图形档案大小可达 300MB,换句话说,一个插满12张数据传输模块的机箱总共会需约260GB的档案大小。

先前提到符合经济效益的产出标准为每6分钟要完成一片晶圆,所以整体上会需要至少725MB/秒的连续数据带宽,通过这样的运作模式,另一组完全不同的晶圆电路图文件,也可在前片晶圆制作完成前可完成下载,以实现少量多样的高性能产出。

总结

凌华科技基于FPGA架构的AXIe 图形传输系统,对于无光罩 E-Beam 微影制程应用,提供高效率集成电路图形数据处理、传输,以及数据同步的解决方案,整体系统跨通道间时钟偏移低于 2ns,且应用AXIe的几项特色,包含可提供大功率电源、有效散热及高可靠度及扩充性,可符合实际半导体生产制程的需求。

关键词: 高速图形传输 PCIe E-Beam 微影技

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码