一种提高微显示器显示分辨率的动态子像素组合方法及FPGA实现

胡子辉,黄嵩人,陈奕星(1.湘潭大学物理与光电学院,湖南省,湘潭市,411105;2.南京芯视元电子有限公司 南京市)

摘 要:增强现实(AR)技术是一种将虚拟信息与真实世界巧妙融合的技术,被视为智能手机之后的下一代终端形态。增强现实其中的一个关键技术就是微显示技术,目前微显示技术发展的瓶颈在于如何使显示芯片尺寸做小而分辨率做高。本文提出了一种提高显示分辨率的动态子像素组合方法,并在现场可编程逻辑门阵列(FPGA)上实现电路。通过对原图像进行数据处理,将一帧原图像分成跟显示屏物理分辨率一致的四个子帧图像,并提高显示帧率,提升了显示屏的显示分辨率,减小了实现同样分辨率显示屏所需要的尺寸,面积减小了44.8%,非常适合应用于微显示领域。

关键词:增强现实;微显示;分辨率;FPGA

0 引言

随着微显示领域,例如增强现实(AR)和虚拟现实(VR)的不断发展,市场对其使用的显示屏的显示质量和尺寸功耗提出了更高的要求。

在众多的显示器中,微型显示器是一种特殊的产品形态,目前业界对其并没有精确定义,通常可以把屏幕对角线尺寸小于30mm的显示器称为微型显示器,简称微显示器或微显示。微显示器自身的物理尺寸很小,但是却可以通过光学系统形成大屏幕显示效果,广泛应用于AR眼镜、微型投影、作战头盔、智慧车灯等场景。一般来说,为了提升显示效果,最直接的方法是增加显示屏的像素数量,来显示更高分辨率的视频或图像。但是,这样做会大幅度增加显示屏尺寸规模和功耗,不适用微显示领域的应用场景。

本文提出了一种提高显示分辨率的动态子像素组合方法,通过对高分辨率的图像进行数据处理后显示在低分辨率的显示屏上,能够在不增加显示屏的功耗和尺寸的条件下使视觉分辨率提升为原来的四倍。特别合适应用于微显示应用场景。

1 方法原理

在显示技术中,显示视频和图像的显示单元被称作为像素。一般而言,显示屏的像素阵列的数目和待显示的视频或图像的分辨率是保持一致的,即待显示视频或图像中的某一像素点会由显示屏上固定的一个像素单元呈现出来。而显示屏的像素单元是由比之更小的子像素组合构成的。一般而言,在显示领域任何一种颜色都可以由红绿蓝(RGB)三种颜色混合而成的,即一个像素阵列其实是由R、G、B这3种子像素按照特定的顺序不断重复排列构成的。

本文通过研究发现,如果可以做到将待显示的高分辨率的图像,拆分成四个低分辨率图像,并在原一帧高分辨率图像的显示时间内,将拆分后的四个低分辨率图像按照特定方式进行显示。通过图像在空间和时间上的累加,可以实现用较低分辨率的屏,显示较高分辨率的图像的目的,并获得优于低分辨率屏的实际显示效果。这种特定的显示方式,在本文被称为动态子像素组合方法。所谓动态子像素组合,相对于传统显示方式,图像的像素单元在显示屏上没有固定的显示单元,在显示过程中显示单元时刻在变化。

1.1 源图像划分

以1080P的视频源做为实验例子,如下图所示,源图像的像素为1080行和1920列,每个像素包含R、G、B三个颜色分量。将1920×1080分辨率的源图像划分成四幅960×540的子图像。具体划分方式为,将奇数行和奇数列的像素依次取出组成子图像1,将奇数行和偶数列的像素依次取出组成子图像2,将偶数行和奇数列的像素依次取出组成子图像3,将偶数行和偶数列的像素依次取出组成子图像4。

1.2 子图像显示方式

为达到更好的显示效果,本文的方案采用当前非常流行的RGBG的显示方式。RGBG的显示方式对比传统的RGB显示方式,每个显示像素单元增加了一个G子像素,由原来的三个子像素增加到四个子像素,显示效果更加细腻平滑。而且采用的是田字型的显示方式,这更方便于动态子像素组合处理。

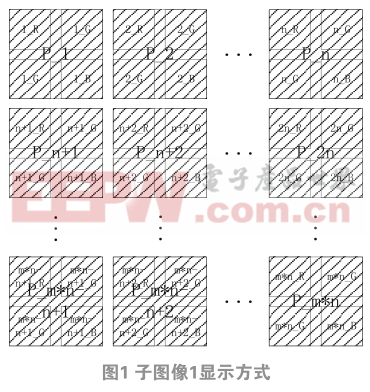

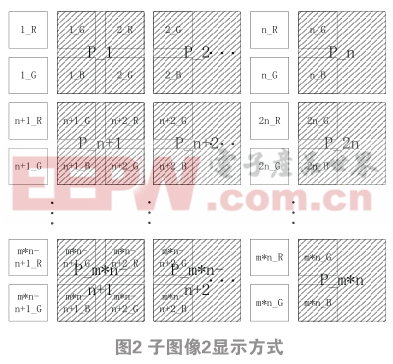

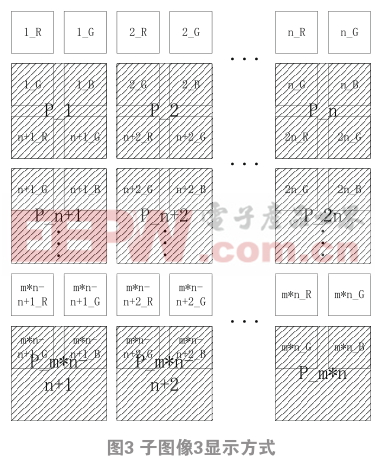

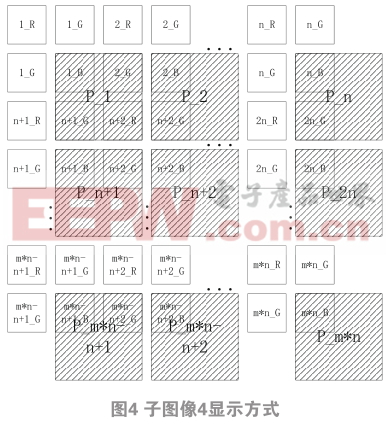

将原视频一帧分成4个子帧,在第一个子帧的时间内,将子图像1按如图1的显示方式显示;在第二个子帧的时间内,将子图像2按如图2的显示方式显示;在第三个子帧的时间内,将子图像3按如图3的显示方式显示;在第四个子帧的时间内,将子图像4按如图4的显示方式显示。最终将四幅子图像都完整的在显示屏上显示出来,并通过提高帧率使四幅子图像的虚拟像素结合,从而提高显示效果。

2 Matlab验证

在matlab中对动态子像素组合的可行性及效果进行验证,该方法期望达到的效果是将四个子帧的图像在时间上叠加显示达到原一帧图像的显示效果。对于图像的像素点而言,每个像素点在四个子图像中分别对应有四个不同的灰度值,灰度值在时间上的叠加效果可以在matlab中取平均值的方式来模拟。

首先对1080P的原图进行划分,不进行动态子像素方法的处理,直接对四幅子图像的灰度值取平均值的方式处理,最后的显示效果的细节如图5中间部分所示,图中左边部分为原图的细节图。将四幅图像经过动态子像素组合方法处理后,再对处理过的四幅子图像的灰度值取平均值后的图像的细节图如图5右边部分所示。

对比原图像、没有经过动态子像素组合方法处理的图像和经过动态子像素组合处理的图像的显示效果可以看出,原图的显示效果显然是最佳的。而四幅子图像直接叠加的显示效果由于分辨率只为原图的四分之一,显示效果模糊了很多。子图像经过动态子像素组合处理的过的显示效果显然比没有处理的图像要清晰许多,但比原图的显示效果还是差了一些。

3 Verilog设计

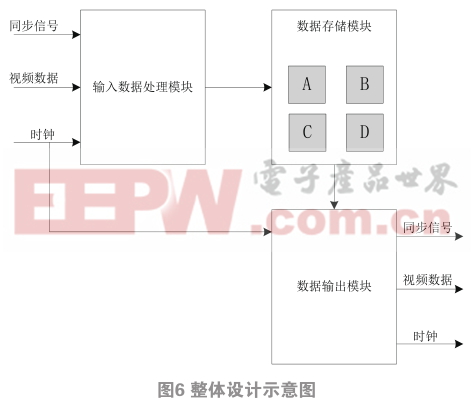

verilog设计要实现的功能是将1080P/60Hz的空间彩色格式的RGB888数据,转化成240Hz/RGBG数据格式输出。如图6为整体设计框图,输入的RGB88数据在输入模块进行处理,实现图像的划分等操作。输入数据把处理过的数据送入RAM中进行缓存,输出处理模块从RAM中读出数据以设定时序输出。

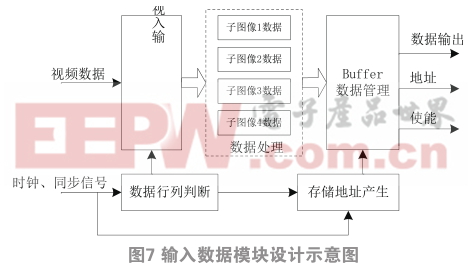

3.1 输入数据模块设计

如图7为输入数据模块设计示意图,输入的RGB888数据每两行都会包含四幅子图像各一行的数据,通过判断行和列的奇偶将数据分开,并分别存入四个存储模块,对于子图像1,显示方式是直接在屏上显示,不需要对数据进行平移处理,直接将数据存入存储模块1。对于子图像2,显示方式是右移一个子像素的距离在屏上显示,所以需要对子图像2的数据进行右移处理后存入存储模块2。对于子图像3,显示方式是下移一个子像素距离显示,所以需要对子图像3的数据进行下移处理后存入存储模块3。对于子图像4,显示方式是向右下移一个子像素距离显示,所以需要对子图像4的数据进行右下移处理后存入存储模块4。

3.2 存储模块设计

如图8为存储模块设计示意图。存储模块共包含4个子存储模块,分别用来存放4个子图像的数据,读写分开,可以同时读和写。写时钟为148.5M,写地址、写数据和写使能由输入数据处理模块提供。读时钟为198M,读地址和读使能由输出数据处理模块提供。

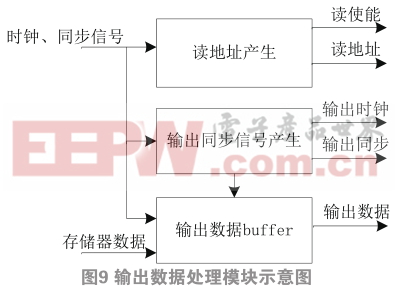

3.3 输出数据模块设计

如图9为输出数据处理模块示意图,功能是读出RAM中的数据,所以需要读使能和读地址信号。由于输出数据格式为RGBG,G颜色分量数据量增加了一倍,所以总的输出数据为输入数据的4/3倍,因此输出时钟应提高到198M,帧率为240Hz,所以需要产生输出时钟及同步信号。

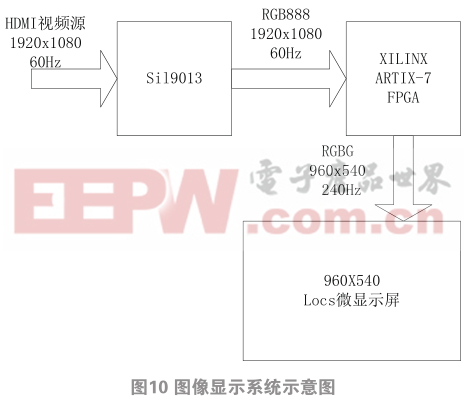

4 FPGA实现

4.1 显示系统

已在XilinxArtix-7系列型号为AX7013的现场可编辑逻辑门阵列(FPGA)开发板上实现了动态子像素组合方法。如图10是用于实现的图像显示系统。通过HDMI接口接入1920×1080分辨率的视频数据,使用Sil9013转换芯片将HDMI数据转成RGB888数据格式,再经过动态子像素组合模块处理,输出960×540分辨率RGBG格式的数据点亮960×540的LCoS微显示屏,显示出1920×1080的图像显示效果。

4.2 显示效果对比

图12左边为图像在LCoS显示芯片上没有经过动态子像素组合方法处理四幅子图像直接叠加显示的细节图,图12右边为图像经过动态子像素组合方法处理的显示细节图。

通过对比可以看出,进行处理的图像的显示效果明显好于没有经过处理的图像。

5 结语

针对微显示应用领域的高分辨率需求,本文提出了一种提高显示分辨率的动态子像素组合方法,通过对高分辨率的图像进行处理,划分成多副子图像显示,并提高显示的帧率,增加了虚拟像素点,提高了显示屏的显示分辨率。此方法经过matlab和FPGA验证通过。通常1080P的微显示屏的尺寸大约为0.7英寸,通过动态子像素组合方法使在0.52英寸的微显示屏上实现了1080P显示。面积减小了44.8%,显示分辨率提高到了原来的四倍。

参考文献:

[1] 马飞,黄苒,赵博华,等.基于FPGA的LCoS显示驱动系统的设计与实现[J].液晶与显示,2012,27(03):364-370.

[2] 耿卫东,代永平,任立儒,等.LCoS场序彩色显示控制器的设计[J].液晶与显示,2003(03):188-192.

[3] 黄成强,李阳军,李春光.应用于AMOLED的RGB到RGBG高速像素转换技术研究[J].光电子·激光,2019(08):850-857.

[4] 严利民,夏明治.一种三基色多子像素排列[J].光电子技术,2017,37(03):182-185.

[5] RUSSELL I A,WALLER C M,EISENBRAND E P. (2017).U.S.Patent No.9,613,573.Washington,DC:U.S Patentand Trademark Office.

[6] GUTTAG K M,WALLER C M,LUNDI A.(2013).U.S.Patent No.8,605,015.Washington,DC:U.S Patent and Trademark Office.

(注:本文来源于科技期刊必威娱乐平台 2020年第05期第51页,欢迎您写论文时引用,并注明出处。)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码