Cyclone IV高速串口在微波数据传输中的应用

编者按:采用ALTERA Cyclone IV FPGA内部SERDES实现多路数据的复分解,舍弃了专用的复分解芯片,在降低系统硬件设计复杂度的同时缩小了PCB板的体积以及系统功耗。利用数据提取、缓存、还原等处理方式,去除异步采样带来的数据传输带宽增加的弊端。实现在有限的无线微波传输带宽、有限的体积内部多种同步异步数据的高可靠性传输。

作者 谢艳1 阳胜波1 陈忠松2 1.中国电子科技集团公司第三十四研究所(广西 桂林 541004) 2.95972部队

摘要:采用ALTERA Cyclone IV FPGA内部SERDES实现多路数据的复分解,舍弃了专用的复分解芯片,在降低系统硬件设计复杂度的同时缩小了PCB板的体积以及系统功耗。利用数据提取、缓存、还原等处理方式,去除异步采样带来的数据传输带宽增加的弊端。实现在有限的无线微波传输带宽、有限的体积内部多种同步异步数据的高可靠性传输。

0 引言

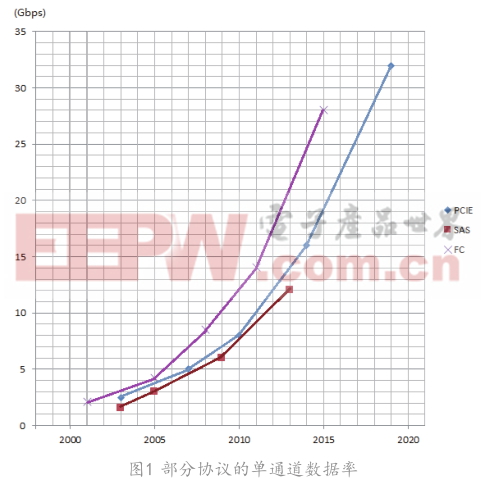

随着通信技术的发展,数据通信的数据传输带宽从2G、3G到4G,光纤通信的数据带宽也从原先的155 M、622 M、1.25 G发展到现在的10 G、100 G甚至是上TB,单波长光缆中传输的数据量越来越大。在无线数据传输方面虽然其传输数据的频率提高了,但是基于无线传输特性,其能提供的信号带宽有限。本文针对系统传输带宽、设备体积功耗有限制应用的场所提出了一种基于ALTERA FPGA的高速串口(SERDES)数据处理、传输解决方案。

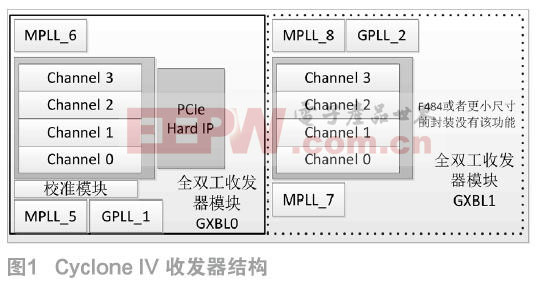

1 Cyclone IV收发器体系结构

ALTERA(已被Intel收购)作为FPGA器[1]件的元老级厂商,其可编程芯片从最初的MAX系列CPLD到低端Cyclone系列FPGA,再到之后的中、高端ARRIA、STRARIX系列FPGA,为数字信号设计、处理提供一系列的从低端到高端的解决方案。从Cyclone系列开始其FPGA就内部自带SERDES(高速串行收发器)软核。

Cyclone IV GX 器件内嵌最多八个全双工收发器,运行在 600 Mbps 到 3.125 Gbps 的串行数据速率上。每个通道都支持PCI Express(PCIE)、千兆以太网(GBE)、通用公共无线接口(CPRI)、串行数据接口(SDI)、Serial RapidIO(SRIO)、串行高级技术附件(SATA)等协议。每四个全双工的收发器通道组成一个收发器模块。

每个收发器通道均由一个发送数据通路和一个接收数据通路组成。每个数据通路又由PMA(物理介质附加子层)和PCS(物理编码子层)两部分组成。其中PMA包括 I/O 缓冲器的模拟电路、时钟数据恢复(CDR)、串行器/解串器(SERDES)以及用于优化串行数据通道性能的可编程预加重与均衡;PCS包括所支持协议的收发器中的数字功能的硬核逻辑实现。FPGA 架构中的输出并行数据通过发送器的 PCS和PMA进行传输,并作为串行数据被发送。接收到的输入串行数据通过接收器的PMA和PCS传输到FPGA架构中。

2 异步数据数据压缩的实现

传统的异步数据(RS-232,RS-422,RS-485,以太网)在通信系统中进行传输主要是采用异步采样的方式来实现,根据奈奎斯特采样定律(2),异步采样的采样时钟(Fs)与被采样数据信号波特率(Fdata)需要满足如下关系:Fs>2Fdata。而在实际应用中一般需要保证采样频率为信号最高频率的2.56~4倍才有可能保证信号的可靠还原。在这种方式下,一个波特率为2 Mbps左右异步数据信号,在不考虑通道开销的情况下,为了实现该信号的可靠传输需要占用的通道带宽最小为5.12 M(2 Mbps×2.56),占用带宽最少是数据实际速率的2.56倍,大大降低了数据传输的通道利用率,对于传输带宽有限的微波信号传输来说是不可取的。

为了解决异步数据传输问题,提高传输通道的利用率,采用数据提取的方式对异步数据信号进行处理,从而压缩数据传输所需的通道带宽。数据提取的核心思想为:采用高速异步时钟,提取出异步数据信号中的有效数据,去除冗余信息。具体实现操作上分串行异步数据(如RS-232,RS-422,RS-485等)和并行的异步数据(如以太网信号等)。

2.1 串行异步数据信号的提取

异步数据如RS-232、RS-422、RS-485等,采用单线串行方式传输,没有与之同步的时钟信号。这些数据只是在电平接口上不同,但是在数据格式上都采用了异步数据的数据格式:即1位低电平起始位+8位数据位+1位高电平停止位的格式,在没有数据时保持高电平状态。其数据格式见图2。

从上图可以看出异步数据大部分时间为固定的高电平,当有数据时以低电平作为起始位,低电平之后的8 bit数据组成一个字节的有效数据,之后又是高电平的停止位以及持续高电平的冗余数据位。这样我们就可以采用异步采样的方式,使用一个高速时钟(在FPGA中具体实现时一般是采用8倍或者16倍的数据速率的采用时钟)对该数据进行提取,具体实现如下:

a)高速时钟对数据进行实时监测;

b)当数据突然由长时间高电平变成低电平,即表示数据到来;

c)此时开始对数据进行采样,持续的采取1bit起始和8bit的数据位;

d)采样第十位数据,并判断该数据是否位高电平,如果高电平,则该次采样数据有效,将采样数据缓存并进入下一个等待周期;如果该位为低电平,则判断该次为误触发,数据无效,丢弃所该次采样数据并进入下一个等待周期。

通过数据提取的方式,从异步串行数据中提取出有效数据,舍弃大部分高电平冗余数据,大大降低了后续数据传输所需的带宽。

2.2 以太网数据的提取

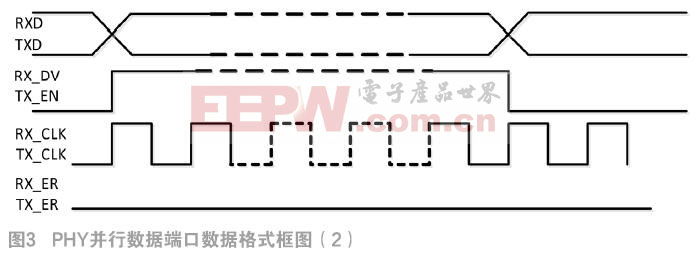

以太网数据是经过网口传输到系统,一般要先经过PHY芯片,实现串行数据流到并行数据流的转换。在不需要关注网络数据内容只需要完成传输任务时,为了降低处理难度,可以直接对PHY接口输出的信号进行处理。一般与PHY连接的MII(百兆以太网)/GMII(千兆以太网)接口数据信号格式如下图。

在数据接收端,网络上的串行数据经PHY芯片转换成并行数据,该并行数据与PHY芯片输出的25 MHz/125 MHz(百兆以太网/千兆以太网)时钟同步,与时钟同步的还有数据有效标志RX_DV,该标志在网络开始有数据时被置高,并且一直保持为高电平直到数据结束;同样以太网接口发数据时只需要将数据保持与发送时钟(TX_CLK)同步,在数据发送期间确保发送使能(TX_EN)保持为高电平。在网络空闲期间RX_DV和TX_EN为低电平,当网络为非全速率时,网络大部分时间处于空闲状态,如果采用异步采样的方式,百兆以太网需要的带宽至少是200 Mbps,而且为了进一步保证信号的正确传输,其异步采样频率还得进一步提高。

由于以太网数据与时钟同步,我们进行数据提取时不再进行异步采样,可以直接使用接收时钟(RX_CLK)对数据进行同步采样,将同步采样到的数据存储到缓存(FIFO)中,当传输时直接从数据缓存中读取数据即可。采用这种方式,即使是100 M全速率的网络,理论上其所需的传输带宽也就只有100 Mbps。

3 基于Cyclone VI 的高速串口数据传输实现

数据提取完成后,下一步是实现数据的传输。目前采用的方法都是将多路数据复用成一路高速串行信号,再通过光纤进行传输。复用主要有采用专用的复用芯片(HDMP1032/1034、TLK15XX(4)等)或者采用FPGA两种方式实现。随着FPGA技术的成熟,在对信号没有特殊要求(实时性、信号抖动、信号时延)的情况下,由于实现的灵活性,FPGA内部自带的SERDES的实现信号复用的方式被越来越多设计人员青睐,。

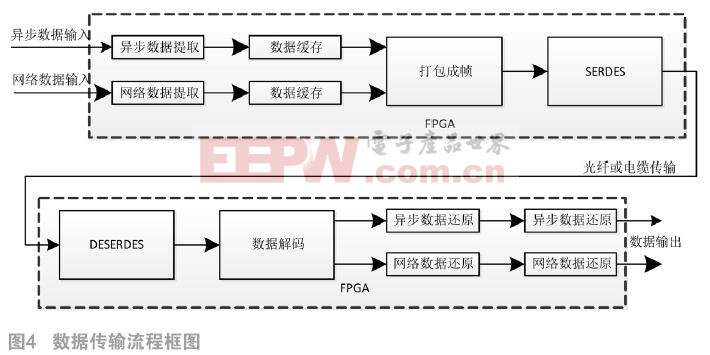

在设计中为了灵活的调整数据所占带宽,对于传输异步数据的缓存也采用FPGA内部FIFO软核实现。从数据输入到最后数据还原输出,其实现框图如下

异步数据及网络数据经数据提取模块,去除传输线路上的冗余数据,保留有效载荷在FPGA内部缓存;之后按照自定义的格式进行打包。数据打包帧格式见图5:主要包含帧界定符、总长度、有效长度、有效载荷及填充数据(冗余载荷)组成。帧界定符定义了一帧数据的起始位置,总长度定义了一帧数据的长度,有效长度表示该帧数据中有效载荷的数量,填充数据(冗余载荷)是为了使高速串口数据速率达到设定的速率而填充的冗余数据。在一个系统中如果所有数据其有效数据量为80 M,如果将SERDES软核串行速率配置成1.25 G,则需要插入约1.17 G的冗余数据。

打包后的数据使用FPGA内部SERDES IP软核对数据包加上K码、实现8 B/10 B变换、并/串转换后以高速串行信号形式通过电缆或者光纤传输(目前一般是采用通用1.25 G、2.5 G或者更高速率光模块实现远距离的光纤传输,Cyclone IV支持的最高速率为3.125G);收端接收到数据后同样使用FPGA内部的SERDES IP软核完成对数据的串/并转换、8 B/10 B解码以及去除k码、Reclock等,完成对数据的解码,通过数据还原恢复出原始速率的异步数据、以太网数据并输出。

4 实现过程中的问题

在实现中考虑到低功耗、小体积、高可靠性的要求,尽可能减少系统中器件的种类及数量,所有数据的FIFO使用FPGA内部RAM实现。但是在具体调试时发现由于以太网网络数据的突发性、不稳定性,传输链路容易在数据量突然增大的时候产生网络丢包的问题。解决这个问题有三种方式:一是增加网络数据缓存,但是由于FIFO使用FPGA内部RAM实现,而FPGA内部资源有限,即使在极限情况都有无法完全解决丢包问题;二是采用外部专用FIFO来进行数据缓存,其存储容量就不受FPGA限制,选用适当的器件,足以满足网络突发数据要求,但是由此带来了系统体积及功耗的增加;三是增加传输数据占用的带宽,但是这种方法对于有限数据带宽的无线微波传输来说,增加了后端无线传输的处理难度。最后在对FPGA程序进行优化,在不改变数据占用的有效带宽的前提下,在FPGA资源利用和网络丢包率之间进行均衡,最大限度的利用FPGA内部存储资源,将系统丢包率降低至≤0.001‰,完全满足了系统网络信号的传输。

5 结束语

紧跟高速串行数据传输的技术发展趋势,利用FPGA内部自带SERDES软核替代以往采用串并转换芯片的硬件解决方案,有效地避开了硬件设计带来的体积及功耗增加等弊端。同时在对数据采用提取、缓存、传输的方式的过程中,将冗余数据去除,高速串行数据通道只传输数据的有效载荷,大大降低高速串行通道中的数据的有效带宽,减小了对后端无线微波直传的数据带宽需求,从而降低了其设计难度及成本,具有一定的实际应用意义。

参考文献:

[1]Cyclone IV 器件手册,卷2Cyclone IV 收发器体系结构: INTEL,2011.11

[2]现代通信原理 第四版:曹志刚 清华大学出版社

[3]Intel LXT971A 3.3v Dual_Speed Fast Ethernet PHY Transceiver datasheet,INTEL 2002

[4]TLK1501 0.6 TO 1.5GBPS TRANSCEIVER datasheet,TI,2002

本文来源于必威娱乐平台 2018年第12期第75页,欢迎您写论文时引用,并注明出处。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码