基于CH7004的VGA接口设计

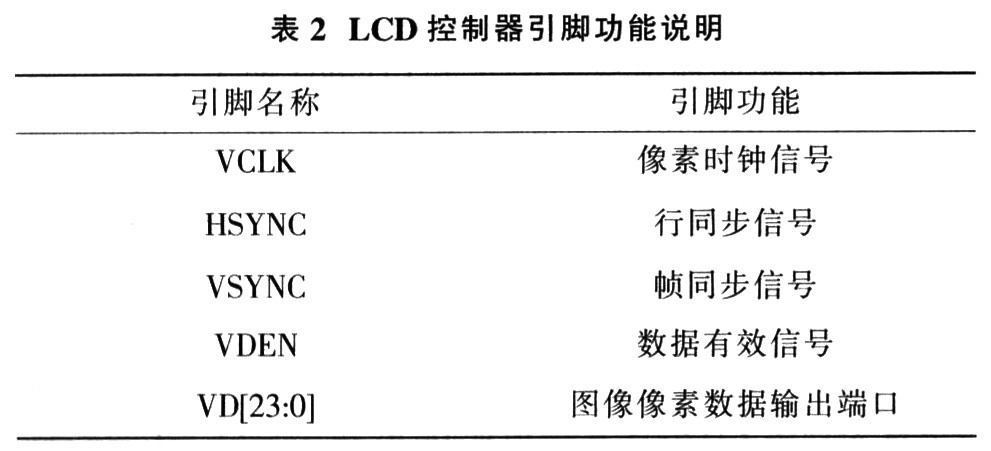

3.1.1 LCD控制器引脚功能

LCD控制器引脚分为时序控制端口和数据端口。与该设计相关的端口具体含义见表2。

3.1.2 LCD控制器内部控制寄存器

LCD控制器内部有5个控制寄存器:LCDCON1~LCD-CON5。LCDCON1控制像素时钟、扫描模式和颜色模式;LCDCON2控制帧同步脉冲宽度、帧有效行数及帧同步前、后的无效行数:LCDCON3主要控制行有效像素点数以及行同步前、后的无效像素点数:LCDCON4主要控制行同步脉冲宽度:LCDCON5主要控制行、场同步脉冲和数据有效信号极性,16位色颜色格式.数据输出与像素时钟跳变关系。

3.2 CH7004器件简介

CH7004是Chrontel公司生产的一款数字转换为模拟的视频编码器,其内部编码器支持NSTL、PAL两种视频制式,通用数字输入接口支持8、 12、15、16和24位数字RGB或者YCrCb格式输入,支持5种图像分辨率,内部集成3路相互独立的高速视频数模转换器,可由用户控制输出模拟 RGB或YUV,提供I2C接口供用户控制器件工作模式。

4 VGA接口设计

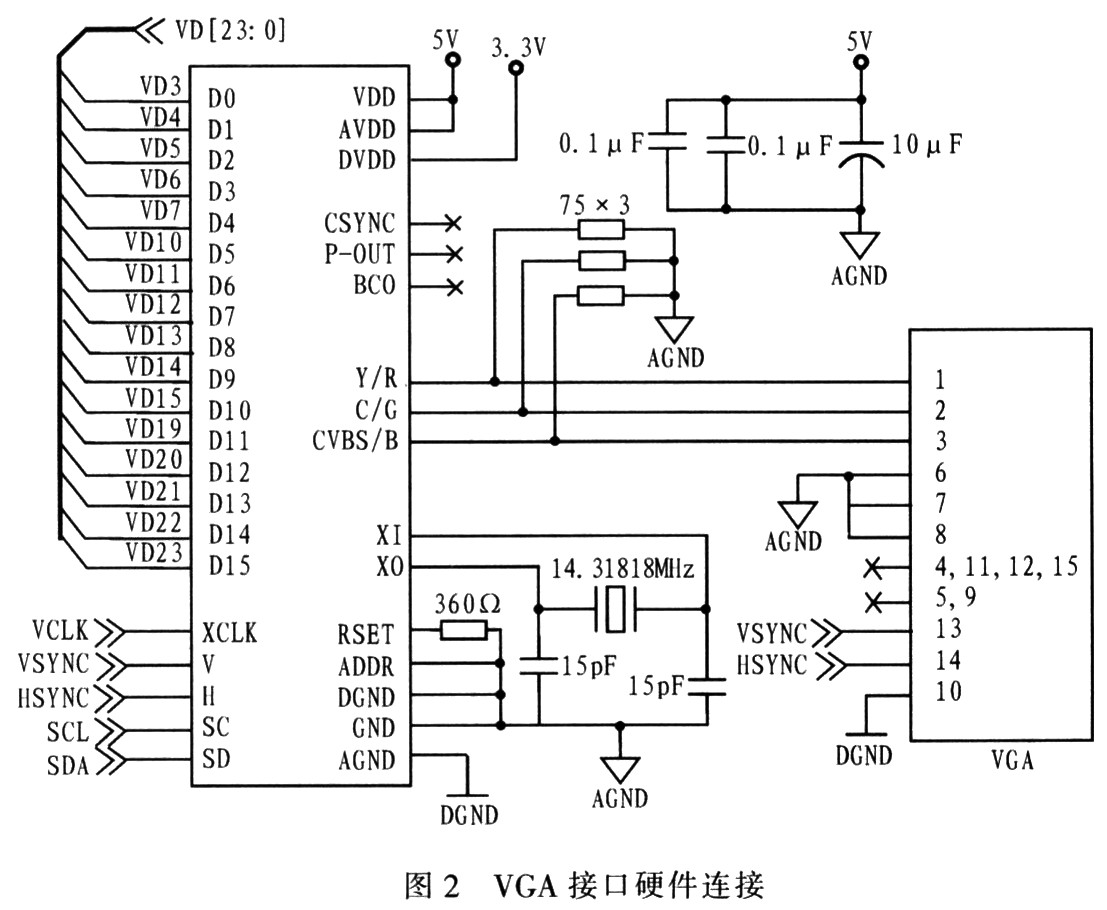

S3C2410处理器的LCD控制器用于产生图像数据、VGA接口时序(640x480,60 Hz)以及配置CH7004的工作模式。CH7004将数字图像数据模拟化,最终产生的模拟图像信号供支持VGA接口的显示器显示。VGA接口的硬件连接见图2。

这里选择(640x480,60 Hz)模式,是由实际需要和硬件特性决定的:(1)嵌入式系统中的图像尺寸大多低于640x480,采用这种VGA模式显示不会丢失任何原始图像信息; (2)VGA的每种显示模式所要求的像素时钟不同,而S3C2410内部LCD控制的像素时钟由器件的主频分频而来,在各种分频后的像素时钟里只有25. 25 MHz(202 MHz主频进行8分频)与VGA模式中的(640x480,60 Hz)模式所要求的像素时钟25.175 MHz最为接近,微小的像素时钟偏差不会影响VGA接口显示;(3)16位色情况下,(640x480,60 Hz)模式数据流带宽为35.2 MB/s,因而不会堵塞S3C2410数据总线,不影响处理器的其他控制、数据处理操作。

CH7004的数据输入端口D0~D15与LCD控制器的相应数据输出端口连接,LCD控制器的像素时钟VCLK通过XCLK端输入CH7004内部, ADDR为低设置CH7004的I2C总线地址,为0x76。CH7004输出端需考虑视频信号阻抗匹配问题,否则会出现图像重影、雪花、或边缘有波纹等问题。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码