高速多通道CCD预放电路设计

2 CCD预放电路的电路板设计

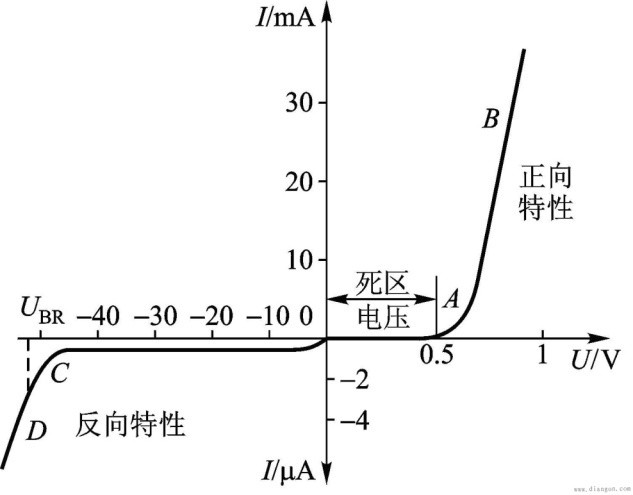

高速运算放大器的电路板设计是电路实现的一个非常重要的部分。即使电路原理设计的再好,随意的电路板设计也会使电路达不到要求甚至产生问题。其中,高速运算放大器的稳定性会受到电路板设计的重要影响。电路板对电路性能的影响产生的主要原因是电路板的寄生参数问题。例如一个运算放大器在电路实现后的等效电路如图3所示。

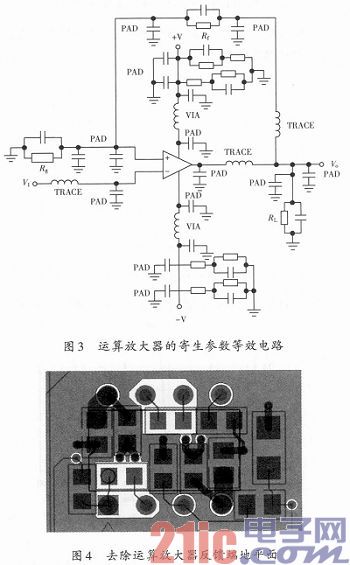

运算放大器的反相端对地电容对放大器的稳定性具有较大的影响。因为反相端的对地电容和反馈电阻Rf在反馈通路上形成了一个额外的极点,该极点使得相位延迟。相位延迟会使得在高频时,负反馈变成了正反馈,从而导致自激振荡。解决这一问题的方法就是把这一寄生电容去除。在具体电路板实现时,就是把反馈端下面的地平面去除。一个双通道的运算放大器布局布线图如图4所示。该放大器为DIP8封装,其中2脚和6脚为两个通道的反馈端。所以2脚和6脚下面的地平面要去除。而反馈电阻焊盘下面的地平面同样也要去除。这样反馈通道中的寄生电容就降到了最低,可以保证放大器的稳定工作。此外,放大器稳定工作和低噪声工作的前提是电源要合理去耦。图4中正负电源的去耦电容都尽可能近地靠近相应电源管脚放置。这样可以有效地降低去耦电路的等效电感,在较宽的频带内提供足够的去耦。

3 实验结果

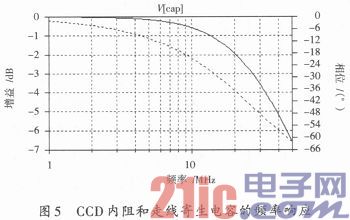

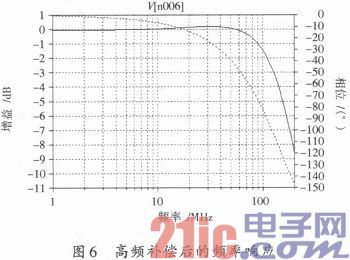

为了验证设计,对设计的电路利用LTspice软件进行了电路仿真。CCD输出等效电阻Rc为300 Ω。走线寄生电容Cp为20 pF。其3 dB带宽只有26.5MHz,其幅频响应和相频响应曲线如图5所示。预放电路的带宽应该为CCD像素转移频率的4~5倍。因此如果像素时钟频率达到25MHz,那么寄生电容就严重限制了电路带宽。所以需要进行高频补偿来展宽带宽。这里Rf取值为1 kΩ,Rg取值为0.28 kΩ,Cg取值为4.7 pF,这时就能满足式(3)的要求。

图6所示为补偿后的频率响应,可见带宽扩展已经超过了100 MHz。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码