兼容特殊视频信号的检测方法

编者按:随着视频处理技术的不断发展,不管是模拟信号或者数字信号都普遍会转换为并行的视频信号进行处理;目前大部分视频处理芯片的接口均是BT1120等类似并行格式,因此对于视频信号的HS和VS的采样显得尤为重要。不同的设计者对VESA标准时序的理解存在偏差,导致经过编码和解码后的HS和VS信号保存了这种偏差。在设备对接时候,如果两家产品存在一定偏差,会导致视频信号出现偶尔轻微抖动。为了解决该问题,本文提出了一种能正常解码此类特殊信号的视频检测方法,增加下游端设备的视频信号兼容性。该方法通过对列同步信号进行的计数,并在

作者 / 林文富 刘伟俭

威创集团股份有限公司(广州 广东 510000)

*基金项目:2014年产学研专项项目经费,支持小间距LED显示的多屏实时处理器系统的研发(编号:2014Y2-00211)

林文富(1982-),男,硕士,中级电子工程师,研究方向:视频处理;刘伟俭,男,博士,中级电子工程师,研究方向:视频处理和显示技术。

摘要:随着视频处理技术的不断发展,不管是模拟信号或者数字信号都普遍会转换为并行的视频信号进行处理;目前大部分视频处理芯片的接口均是BT1120等类似并行格式,因此对于视频信号的HS和VS的采样显得尤为重要。不同的设计者对VESA标准时序的理解存在偏差,导致经过编码和解码后的HS和VS信号保存了这种偏差。在设备对接时候,如果两家产品存在一定偏差,会导致视频信号出现偶尔轻微抖动。为了解决该问题,本文提出了一种能正常解码此类特殊信号的视频检测方法,增加下游端设备的视频信号兼容性。该方法通过对列同步信号进行的计数,并在VS有效期间做差值,作为判断有效的行数,规避了常规检测方法带来的误差。验证结果显示,采用该种特殊的视频检测方法,可以有效去除视频的抖动,大大增加了下游视频解码端的兼容性。

1 视频HS和VS的标准时序

在VESA标准里边,定义了4种信号,分别是PCLK、DE、HS和VS,这四种信号虽然没有包含视频数据,但是非常关键。Pclk是视频的像素时钟,用于在有效的DE区间采样视频数据。DE表示有效数据选通信号也称数据使能信号,在液晶显示器电路中其表示符号有多种,如DSP、DSPTMG、DEN、DE等,一般称其为DE信号。其中HS表示行同步信号,VS表示场同步信号。在显示设备中,行同步信号(HS)的作用是选择出显示器上有效行信号区间,场同步信号(VS)的作用是选择出显示器上有效场信号区间,行场同步信号的共同作用,可将选择出有效视频显示区域。

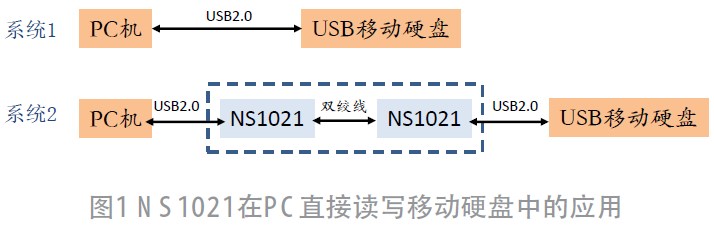

下图1所示为VESA标准时序图[1],VS和HS可为正极性和负极性。一般来讲,在VS的有效区域的跳变沿开始计算HS,图1中VS的上升沿开始表示场同步信号有效,在VS的下降沿表示场同步信号开始无效。一般计算一帧内有多少行,就是通过计算在有效的VS区间,有多少个有效的HS数量来确定。以1080P的分辨率为例,一般水平像素点个数为2200,有效像素点个数为1920;垂直行数为1125,其中有效的行数为1080,其他包含了消隐期。

2 视频抖动产生的原因

目前的数字视频信号DVI、HDMI等,大多采样TMDS编码传输,通过差分对传输方式可以进行长距离传输,并且抗干扰性强。它和LVDS、TTL相比有较好的电磁兼容性能,可以用低成本的专用电缆实现长距离、高质量的数字信号传输。TMDS传输系统[2]分为两个部分:发送端和接收端。TMDS发送端收到HDMI接口传来的表示RGB信号的24位并行数据(TMDS对每个像素的RGB三原色分别按8bit编码,即R信号有8位,G信号有8位,B信号有8位),然后对这些数据进行编码和并/串转换,再将表示3个RGB信号的数据分别分配到独立的传输通道发送出去[3]。接收端接收来自发送端的串行信号,对其进行解码和串/并转换,然后发送到显示器的控制端。与此同时也接收时钟信号,以实现同步。这种编码方式,对应DE、HS和VS信号,同样也是对其进行编码,通过第0通道进行传输。

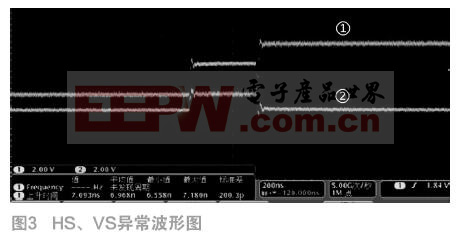

如图2所示,视频图像在TMDS编码芯片中进行编码,转成DVI或者HDMI信号进入传输。通过线缆进入了下游的视频图像处理设备,图像经过缩放或者旋转处理后,输出到显示器进行输出显示。在这个传输路径中,如果在起始位置出现HS和VS的相对位置发生偏移,通过TMDS的编码和解码后,这种位置偏移任然活传送到下游的视频处理设备。从下游视频处理设备的显示输出看,会出现视频的抖动现象。在上游视频输出设备,见箭头处,由于不同的设计者对VESA标准的理解不一样,HS和VS发生相位偏差或者出现类似图3情况(①为VS,②为HS)均有可能。

3 新的视频检测方法

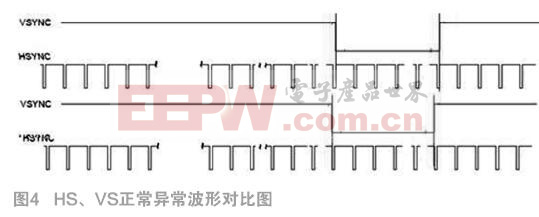

一般的列同步宽度检测方法是在VS和HS进入后,首先对其进行极性归一化,即是统一成VS低电平有效,HS高电平有效;归一化后,采用边沿触发计数方式,在VS的下降沿开始计数列同步宽度和时间,在VS的上升沿保存计数值和清零。该种方式在正常的时序中对列同步宽度的判断是没有问题的,但是在上述异常现象中,通常会出现列同步宽度计数错误。具体见图4,上面波形为异常波形,相当与VS的相位延迟了一定角度,采用一般的视频检测方法,将会导致第一个HS无法计数,列同步宽度和总时间少计算一行,累积到一定程度图像出现轻微抖动。图4中,下面的波形为正常波形,当VS的下降沿开始时候,是可以正常计数到第一个HS的,不会出现处理后的图像抖动现象。

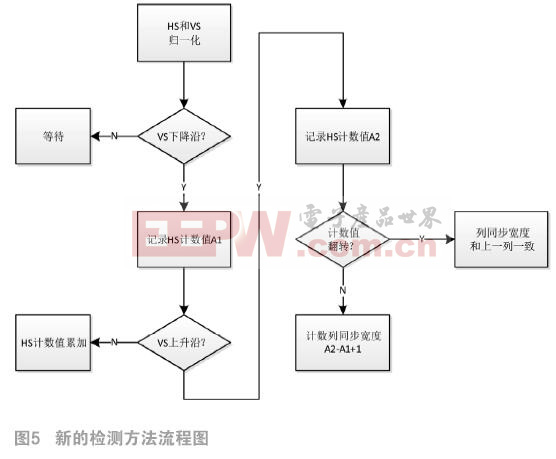

为了解决上述的HS和VS相位发生异常问题,本文提出一种新的检测HS行数的方法。该方法针对普通方法的一种改进,改进点主要是采用了不依赖相位的办法,通过在VS的有效区间内,计算HS的差值方法来实现对列同步宽度的正确统计。该方法的主要实现流程见图5,首先也是对HS和VS进行归一化,相当对HS和VS的极性进行统一,实现对不同极性的信号采用同样的统计方法;判断VS的下降沿是否到来,如果没有,表示有效的VS区间还没有开始,进行等待,如果下降沿到了,开始对HS进行计数,并且记录下此时的数值A1;判断VS的上升沿是否到来,如果没有,数据进行累加,如果到了,记录此时的数值A2;因为记录数值的寄存器是有一定的位数限制,可能会出现计数满了归零情况,所以,此时要对该情况进行判断,若发现A2小于A1情况,则是出现了翻转,此时默认列同步宽度和上次记录是一样的,若没有出现翻转,则计算列同步宽度为A2-A1+1。采用该种计数方法,可以有效避免一般检测方法的缺陷,提供视频处理设备的兼容性。

4 结论

本文根据目前的一些视频信号有异常或者不完善的情况,提出了一种新的视频列同步检测方法。该方法和一般的检测方法不同在于它可以避免HS和VS相位差异带来的计数错误问题,采用了相对差值的办法来统计列同步宽度。该方法在实践应用中效果良好,有效地解决了几个工程项目中出现视频信号时而抖动问题,大大增加了显示端视频处理设备的兼容性,具备很高的实用价值。

参考文献:

[1]Proposed VESA and Industry Standards and Guidelinesfor Computer Display Monitor Timing (DMT) Version 1.0.

[2]苗绘玲.视频时序信号发生器的实现方法[J].电视技术,2016,40(10):45-49.

[3]KEITHJ.视频技术手册[M].第5版.杨征,田尊华,张杰良,等,译.北京:人民邮电出版社,2009.

本文来源于必威娱乐平台 2018年第1期第66页,欢迎您写论文时引用,并注明出处。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码