LED芯片漏电原因深度解析

LED漏电的问题,有很多人都遇到过。有的是在生产检测时就发现,有的是在客户使用时发现。漏电出现的时机也各有不同。有些是在LED封装完成后的测试时就有;有些是在仓库放置一段时间后出现;有些是在老化一段时间后出现;有些是在客户焊接后出现;有些是在客户使用一段时间后出现。而对漏电问题的具体发生原因,一直困扰着封装厂的工程师。

LED漏电的原因

在引言部分,罗列了一些人给出的造成LED漏电的原因。根据本人多年处理LED问题及使用LED的经验,本人认为,在目前,最可能导致LED发生漏电的主要原因排序应该如下:

(1)芯片受到沾污 (——最主要、高发问题)

(2)银胶过高

(3)打线偏焊

(4)应力

(5)使用不当

(6)晶片本身漏电

(7)工艺不当,使得芯片开裂

(8)静电

(9)其它原因

本人将静电问题几乎排到了最后,几乎颠覆了行业乃至专家的认识。为什么把静电问题排在了最后,后面再谈详细原因。

对LED漏电原因的分析:

1. 芯片受到沾污引起漏电

LED芯片是非常小的,灰尘等易对它产生遮蔽作用,最重要的是灰尘、水汽、各种杂质离子会附着与芯片表面,不仅会在表面对芯片内部产生作用,还会扩散进入芯片内部产生作用。比如,铜离子、钠离子都很容易扩散进入半导体材料中,非常微小的数量就可以使半导体器件的性能严重恶化。对于半导体器件的制造,通常都要求有净化等级非常高的洁净厂房。可以考察一下LED封装厂,上千家之中有几家的厂房能有什么样的洁净等级?绝大多数都是能与大气直接相通的房间,根本谈不上净化。虽然有人会说,“我们的厂房没有灰尘,很洁净”,可是,洁净程度不是用眼睛来看的!眼睛是根本看不到芯片生产和封装要求的洁净程度的,必须是用专门的仪器来检测。不仅仅要求厂房要达到要求的洁净度,对涉及到芯片裸露的工序,工作人员要穿净化工作服,戴工作帽,戴口罩,工作人员不许涂化妆品等。这些个严苛生产条件,目前对LED封装厂来讲,不是想不到,就是不愿做。不愿做的原因非常简单,成本上的增加无法接受——竞争太激烈。封装厂房达不到要求的洁净程度,那么,LED的质量问题就来了。

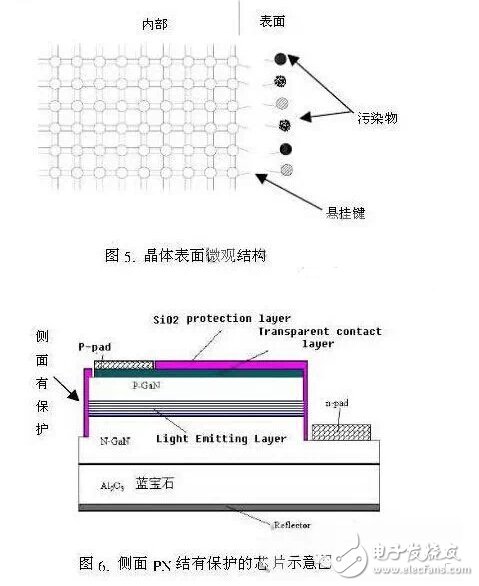

早期的LED芯片以及现在很多厂家的芯片,都没有在芯片的侧面做保护层。现在国外一些芯片厂商已经开始在芯片的侧面做保护层了。但是,现在的保护层一般是采用二氧化硅材料,而且厚度很薄,保护能力是有限的。在洁净度很差的封装厂,仍然会由于沾污造成漏电现象。

下面我们来做分析。

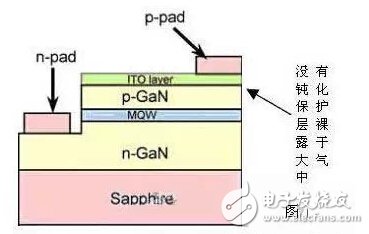

1.1 芯片侧面没有做钝化

很多芯片由于各种因素,没有对芯片的侧面做钝化保护,使得芯片划片后,PN结在侧面裸露于空气中。如图1所示。

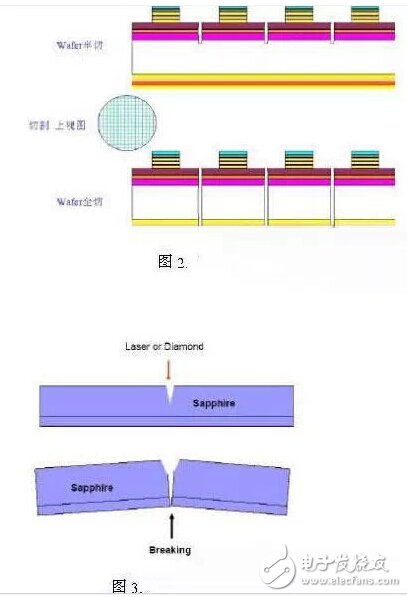

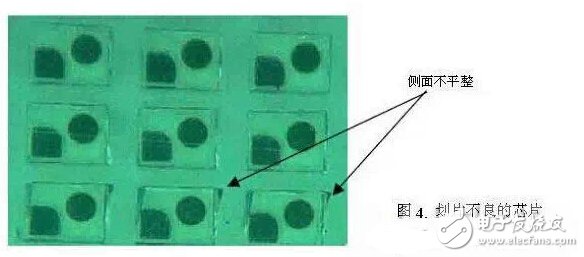

以前未作侧面钝化的圆片,划片方法见图2和图3.从图4对实际芯片包装的照片上就可以证明芯片侧面是不做钝化的。因为从照片上可以看到,芯片侧面极不规整。为什么这样芯片还可以出厂呢?因为,在芯片厂里,侧面即使没有保护层,由于厂房的洁净度高,加之裸露时间不长,侧面还没有受到沾污,所以测量是没有漏电的,就将它们出厂了。

为什么这样的状况就会造成漏电呢?下面就要从微观结构上来讲讲了。

图5是一个晶体表面处的微观结构示意图。表面处原子外层电子数不饱和,存在悬挂键。这些悬挂键形成表面态能级,引起漏电【3】【4】。而且,这些悬挂键非常有活性,很容易吸附其它分子、原子和离子。所吸附的杂质发生电离,直接就形成了电流通道。这个电流通道相当于给PN结并联了一个电阻。

这种表面沾污造成的漏电及短期失效问题,早已被半导体元器件制造行业认识,并通过制作保护层来加以解决。

1.2 芯片侧面有保护层

现在有些LED芯片厂在芯片侧面也做上了二氧化硅保护层。但是,即使是PN结端面上有二氧化硅保护层,由于制造方面的原因,在二氧化硅中可能会有可移动的离子存在。在封装厂的不洁净环境中,还会收到沾污。所以,没有良好的二氧化硅生产工艺,没有达到洁净等级的封装厂房,LED封装后出现漏电的几率仍然是很高的。

二氧化硅层中的可移动离子移动到半导体材料表面,可能使P型材料表面产生耗尽层,严重的发生反型,从而发生漏电。

在通常的硅半导体器件制造中,为了解决二氧化硅的问题,一般会在芯片功能制造完毕后,再增加一层钝化层。现在常用的是氮化硅材料。这样会大大提高半导体器件的稳定性和可靠性【5】【6】。这些不是本文讨论的内容,提及它只是提醒大家,在LED中,虽然有二氧化硅保护层,但后期不注意保洁,还是会有漏电问题的。

对于二氧化硅中含可移动离子及沾污对漏电的更详细的分析,读者可以参考有关半导体的资料,如半导体物理、晶体管原理、半导体器件制造工艺等书籍。

1.3 沾污漏电的表现

晶体管的漏电,可能是PN结制造不良产生,也可能是沾污造成。通常,PN结不良或受损产生漏电是不可恢复的,具有正、反向漏电状况基本相同的特征,而且常表现为完全穿通。沾污造成的漏电,观察其伏安特性,通常有多种表现,如:正、反向漏电的伏安特性曲线不同;反向击穿电压蠕变;正向伏安曲线蠕变;严重的也会表现出正、反向都是穿通的状况等。沾污漏电还表现出不稳定性,某些状况下,漏电状况还会暂时恢复正常,即暂时不漏电。

下面通过一些实例来看看沾污对LED带来的漏电表现。

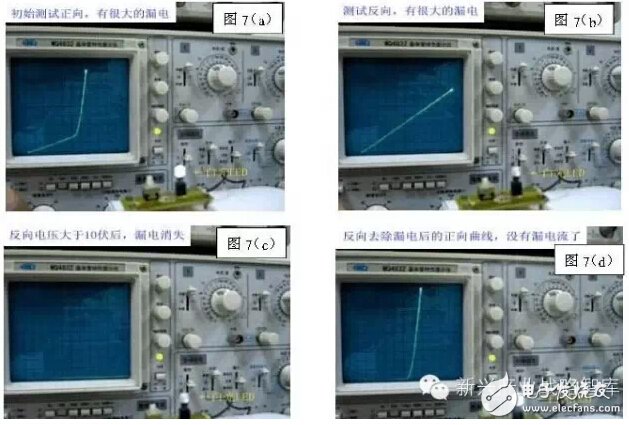

实例一:被反向电压击正常的LED

白光LED,测试正向时,有漏电,见图7(a)。测反向时,在反向电压小于某个值时,可以看到有很大的漏电,图7(b)中的反向电压为10V。当着反向电压继续增大时,漏电突然消失,呈现不漏电的状况。图7(c)中漏电消失时的发现电压约大于10V。此时再测试正向伏安特性,可以看到,漏电完全消失,LED恢复正常。见图7(d)。但是,这种恢复正常是暂时的,放置一段时间后,LED又会出现漏电。测试时,还会重复上述过程。

从正、反向的漏电曲线看,它们的漏电程度是不同的。这种反向电压击正常的现象,分析为外加电场使得沾污离子的再分布,使其远离PN结端面区域。因而使得PN结端面恢复正常。但是放置一段时间,由于温度的变化,或在正向电压作用下,沾污离子又会迁移到PN结端面附近,重新造成漏电。

实例二、反向电流蠕变,较高反电下漏电消失。读者可以先看一下附件1的实测视频——反向电压击正常的LED。在此示例中可以看到,在施加反向电压时,随着电压的升高,反向电流忽大忽小,即发生蠕变现象。当着反向电压高到某个值时,漏电流消失了。再测正向特性,可以看到是正常的,没有漏电流了。不过,这种恢复正常也是暂时的,放置一段时间后又会恢复漏电状况。

实例三、反向漏电蠕变非常大,正向漏电蠕变,到VF时不漏电。读者可以先看一下附件2的实测视频——大漏电会亮的LED。本例与实例一不同的是,在较高反压下也没能使漏电消失,并且反向漏电非常大。但是在正向时,漏电并没有反向的大,在正向导通后,漏电状况反倒消失了。

实例四、反向漏电不是很大,正向电压小于VF时漏电很大,到VF之后漏电变到很小。读者可以先看一下沾污漏电。

实例五、正向点亮前漏电非常大,到VF时基本正常。而反向漏电远比正向漏电小。读者可以看一下LED非击穿漏电。

实例六、LED产品严重漏电,类似穿通。解剖出芯片后,芯片正常,没有漏电。

1.4 沾污漏电的判定

沾污漏电和PN结或体材料受损漏电的区分,有些状况很难直接判定,需要解剖取出芯片来观察分析。但是,有些现象确实可以区分的。比如上面的六个实例中都是沾污造成的漏电。

1.5 本节小结

沾污漏电,PN结没有损伤,它是由于沾污离子直接或间接参与导电形成的。这种状况在半导体制造行业中是一个常识性的问题,已经有很多表面钝化方法可以很好地解决。LED行业虽然也是属于半导体行业,但是就LED封装行业来看,由于技术门槛低,使得这个行业中有半导体专业知识的人员非常少。结果一个很普通的、常识性的问题,在LED行业中成了一个难以克服的问题。之所以难以克服,就是因为没有找到问题的症结。而是一味听信于一些“专家”对静电问题的夸大宣传。结果是花费了大量资金和精力于防静电上。防静电措施做得非常好了,可是漏电现象依然发生。

在前面已经提到了,绝大多数的封装厂的生产环境非常差,没有净化厂房,LED漏电现象是在所难免的。所以有些人会说到,入库产品每隔几天拿出来测试就会发现有漏电的产品出现。“净化厂房”可不是指用拖布拖得干干净净的、底板非常亮的就是净化厂房。在LED的固晶、焊线、封胶等工序中,由于芯片会裸露于空气中,所以必须要有达到一定等级的净化程度。净化等级是要用仪器来测量确定的,绝不是用眼睛能看到的。

静电的状况是随机的,虽然它似乎无处不在,但它绝不是处处都能够释放足够的能量造成破坏。

2. 银胶过高造成漏电

这个问题在LED封装业中已是常识性的、看得见的问题了,无需我多啰嗦了。

3. 打线偏焊造成漏电

这个问题在LED封装业中也是常识性的、看得见的问题了,也无需我多啰嗦了。

4. 应力造成漏电

应力,往往是看不见的,若对材料的一些基本性质不了解,则不太好理解这个问题。其实,应力相对于日常可见的比如推土机推土那样大的力相比,它是很难看得见的作用力而已。它往往是由于材料的热胀冷缩而产生。应力的影响往往是在两种材料的接触方面。应力作用可以是直接压力,也可以是与材料接触面平行的横向剪切力。举一个简单的例子,在两根铁轨之间是有一段间隙的,如果将这个间隙留的很小,当温度升高时,两段铁轨的端面就会接触,甚至挤压变形。这就是应力作用。当两种不同的材料粘结接触时,当温度发生变化,若两种材料的热膨胀系数不同,在接触面由于延伸或收缩尺度不同,相互间产生拉力,这就是横向的剪切应力。

在LED中,有不同的材料,热膨胀系数是不同的。在温度反复变化的过程中,各物质不可能回复到它们最初接触时的状态,相互间会保持有一定的应力。但不一定会有害。只有当膨胀系数相差太大、工艺条件不合适时,就可能留下很大的应力。这个应力严重的会压坏芯片,使芯片破损,造成漏电、部分区域裂开而不亮,严重的彻底开路不亮。应力不是很大时,有时也会产生严重的后果。

原本在LED的侧面就存在着悬挂键,应力的作用,使得表面原子发生微位移,这些悬挂键的电场更加处于一种不平衡状态,从而造成端面PN结处的能级状态发生改变,造成漏电。

5. 使用不当造成漏电

这种状况一般较少发生。当较高的反向电压加给LED,可能损坏PN结,造成漏电。

这种损坏,和静电损坏的机理是相同的。如果不是当事人自己确认,封装厂的工程师单凭损坏的样品来看,是很难分辨的。

6. 芯片本身漏电

通常,这种情况也是较少发生。除非芯片的次品出厂。

一般来讲,芯片在制造厂是不容易受到沾污的。但是,在芯片的后续分选、包装时,是有可能发生沾污的。本人看到过某芯片厂的后续分选、包装车间环境就是没有净化等级的普通厂房。

7. 工艺不当,使得芯片开裂

芯片底部胶体不均匀,或焊盘下面有空洞,打线时可能损伤芯片产生漏电或失效。 焊线机调整不当,打伤芯片,产生漏电或失效。

8. 静电问题

在LED行业,似乎将静电当成了损坏LED的头号大敌。但本人却不这么认为。相反,将它当成次要问题。

对于静电对LED的损坏问题,本人在一些论坛里有谈过【7】。现在将那些内容搬过来,并加以补充,以便大家阅读与了解。

8.1 静电的产生机理

通常,静电的产生是由于摩擦或感应而产生。

摩擦静电是由于两个物体接触摩擦或分离过程中产生电荷的移动而产生。导体间的摩擦留下的静电通常比较弱,这是由于导体的导电能力强,摩擦产生的离子会在摩擦过程中及终止时很快运动到一起而中和。而绝缘体摩擦后,可能会产生较高的静电电压,但是电荷量却很小。这是由于绝缘体本身的物理结构决定的。绝缘体的分子结构中,电子很难脱离原子核的束缚自由移动,所以,摩擦结果也只能产生少量的分子或原子电离。

感应静电是物体处于电场之中,受电磁场的作用,物体中的电子发生移动而形成电场。感应静电一般只能在导体上产生。空间电磁场对绝缘体的作用可以忽略。

8.2 静电的放电机理

220V的市电可以打死人,可人们身上上千伏的电压却打不死人,是何道理? 电容两端的电压满足下列公式:

U=Q/C

根据这个公式可以知道,当电容量很小时,很少的电荷量,就会产生很高的电压。

通常我们的身体、身边的物体,电容都非常小,当产生电荷后,很少的电荷量,也会产生很高的电压。

由于电荷量很少,放电时,形成的电流非常小,时间非常短,电压不能维持,极短的时间就降下来。

由于人体不是绝缘体,所以,身体各处积累的静电荷,在有放电通路的情况下,都会汇集过来,所以感觉电流大些,有电击的感觉。人体、金属物品等导体在产生静电后,放电电流会比较大。

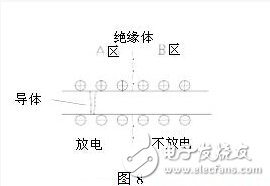

对于绝缘性能好的材料,一个是产生的电荷量非常小,另一方面,产生的电荷,很难流动。电压虽然高,但某处有放电通路时,只是接触点及附近极小范围内的电荷可以流动放电,非接触点的电荷则不能放电(谁叫它是绝缘体呢)。故而,就是有上万伏的电压,放电能量也是微乎其微的。如图8所示。

所以,虽然塑料周转箱、包装泡沫上、化纤地毯等的静电电压非常高,其实放电能量非常小。

8.3 静电对电子元器件的危害

静电会对LED有危害,并不是LED独有的“专利”,就是用硅材料制造的常用的二极管、三极管,也都会受到威胁。甚至建筑、树木、动物都可能被静电损害(雷电就是一种静电,我们这里就不去考虑它了)。

那么,静电是怎么对电子元件损害的呢?我也不要扯得太远,就只讲半导体器件的问题,而且就局限于二极管、三极管、IC、LED方面。(否则会啰嗦太多冲淡主题)。

电对半导体元器件的损坏,最终是有电流的参与。在电流的作用下,由于热而损坏器件。要有电流,就要有电压。但是,半导体二极管有PN结,无论是正向还是反向,PN结都会有阻挡电流的一个电压范围。正向势垒低,反向势垒则要高很多。在一个电路中,哪里的电阻大,电压就在哪里集中。但就来看LED,电压正向加给LED时,当外电压小于二极管的阈值电压(大小与材料禁带宽度对应),没有正向电流,电压全部加在PN结上。电压反向加给LED时,当外电压小于LED的反向击穿电压时,电压也是全部加在PN结上,此时,LED的虚焊点也罢,支架也罢、P区也罢、N区也罢,统统都没有电压降!因为没有电流。当着PN结击穿后,外电压才会由电路上的所有电阻分担。哪个地方电阻大,哪个部分承担的电压就高。就LED而言,自然是PN结承担了大部分电压。在PN结上产生的热功率就是它上面的压降乘以电流值。若是电流值不加限制,过高的热量就会将PN结烧坏,PN结失去作用而穿通。

IC为什么会比较怕静电,因为,IC中的每个元件的面积非常小,每个元件的寄生电容也就非常小(往往电路功能就要求寄生电容非常小),所以,少量的静电电荷就会产生很高的静电电压,而且每个元件的功率耐量通常也很小,所以,静电放电就很容易损坏IC。但是通常的分立元件,如普通的小功率二极管、小功率三极管都不是非常怕静电,因为它们芯片的面积比较大,寄生电容也比较大,一般的静定不容易在它们上面积累高电压。小功率的MOS管,由于栅极氧化层很薄,寄生电容小,所以很容易遭静电损坏,通常会在封装完成后将三个电极短路后出厂。使用中也常要求在焊接完成后再去掉短路线。而大功率的MOS管,由于芯片面积大,一般的静电也不会损坏它们。所以你会看到,现在功率MOS管的三个电极是没有短路线保护的。(早期制造厂还是将它们短路后出厂的)

LED实际就是有个二极管,它的面积相对IC内的每个元件来讲,是非常大的。所以LED的寄生电容相对来说也是比较大的。所以,一般场合的静电并不能损坏LED。

一般场合的静电,尤其是绝缘体上产生的静电,电压会很高,但放电电荷量极微,而且放电电流持续时间很短。而导体上感应的静电,电压可能不是很高,但是放电电流却可能很大,而且往往是持续的电流。这样对电子元件的危害就非常大。

8.4 为什么说静电对LED的损害是不常发生的呢

先来看一个试验现象。一块金属铁板上带有500V的静电,将LED放到金属板上(放的方法要注意,避免下述的问题发生),大家说LED会被损坏吗?这里,LED要被损坏,通常应该是被加上大于其击穿电压的电压,也就是说LED的两个电极要同时接触金属板,并具有大于击穿电压的电压。由于铁板是良导体,其上各处的感应电压相等,所谓500V的电压是相对于地而言的,所以,LED两电极间是没有电压的,自然也就不会受到任何损伤了。除非,你将LED 的一个电极接触铁板,另一个电极你用导体(未戴绝缘手套的手或导线)连接到地或其它导体上。

上面的试验现象提示我们,LED在静电场中时,必须是一个电极接触静电体,另一个电极要接触地或其它导体才可能受损。在实际生产和应用中,以 LED那么小的体积,很少有机会发生那样的事情,尤其是批量发生那样的事情。偶然的事件是可能的。比如,LED处于静电体上,且一个电极接触到静电体,另一个电极刚好是悬空的,此时有人去触及了悬空的那个电极,就可能损伤LED。

上面的现象告诉我们,静电问题也不是可以忽视的。 静电放电是要有导电回路的,不是有静电就有损害。

上面的现象还提示我们,当着仅有极少量的漏电问题发生,可以考虑静电偶然损坏问题。若是大量发生,则更多的可能是芯片沾污或应力的问题。

9. 其它原因引起漏电

本人曾遇到过这样的漏电状况,LED被封装与一个壳体中,LED周围灌有软胶以防水。可是从LED的引线上测到有严重的漏电。将周围的灌封胶去除后,漏电消失。这里其实并不是LED漏电,而是灌封胶有问题。

后记

对于LED的漏电问题,大部分项大家基本没有什么异议。而对于芯片沾污和应力造成漏电,LED行业不了解的人想必很多。尤其是LED经过客户的手后再反映漏电,封装厂和芯片厂都会归咎于静电,理由是它们在出厂时是没有漏电的。这其实就是因为沾污或应力问题的存在而导致的可靠性问题,具体就是早期失效问题。很多封装厂的工程师不了解这些。因为非常多的封装工程师不是学习半导体器件专业的。

有些不了解的人还会把漏电原因归结于封装厂使用了烂芯片,封装厂也会感到很委屈。(确实有用烂芯片的,这个也不排除)。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码