3系列FPGA中使用LUT构建分布式RAM(1)

前一阵出差,然后又吹空调受凉休息了一阵子,耽误了不少时间。现在缓过劲来了,可以继续写作了。出差途中数小时路上无聊,就顺手打印了XAPP463.pdf,即《Using Block RAM in Spartan-3 GeneraTIon FPGAs》,深感FPGA配置的灵活与复杂性。在此把阅读此应用报告的心得分享一下,欢迎大家交流。

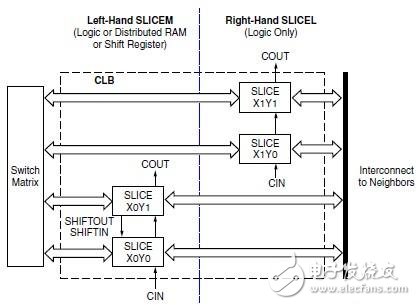

在赛灵思Spartan-3、3E等系列的FPGA中,其逻辑单元CLB中一般含有不同数量的单端口RAM(SRAM)或者双端口RAM(DRAM),这里的“单”或者“双”是由我们开发人员定义的。一般情况下这种RAM分布于(distributed)FPGA的阵列结构中,所以被称为“分布式RAM”,以便区别于FPGA中的块RAM(block RAM);它们的详细区别大家可以看Spartan3系列的用户手册(UG331.pdf, Spartan-3 GeneraTIon FPGA User Guide),其中对所有模块及其功能都有最全面的解释,包括各种复杂的时序分析。分布式RAM在局部设计中可以方便地实现小的数据缓存区、FIFO或者寄存器组等等。接下来我们讨论分布式RAM的特征、功能以及如何使用Xilinx的工具来调用分布式RAM。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码