基于OR1200的SoC程序无线智能加载系统设计及验证

编者按:SoC是当前微电子芯片发展的趋势,然而由于受带开发环境的PC终端、额外硬件接口、连接线等条件的约束,很难支持SoC产品的二次开发。本文提出一种SoC无线程序加载系统设计方案,通过无线控制实现不同程序的加载,不需要添加额外的接口与复杂的模块,不需要连接下载线和IDE开发环境等工具,简化了芯片的二次开发,增加了芯片的利用率。并且在FPGA板上测试通过。

作者/ 黄诚1 唐明华2 1.湘潭大学 物理与光电工程学院(湖南 湘潭 411105) 2.湘潭大学 材料科学与工程学院(湖南 湘潭 411105)

*基金项目:国家自然科学基金(编号:51472210)

黄诚(1992-),男,硕士生,研究方向:数字电路SoC设计等。

摘要:SoC是当前微电子芯片发展的趋势,然而由于受带开发环境的PC终端、额外硬件接口、连接线等条件的约束,很难支持SoC产品的二次开发。本文提出一种SoC无线程序加载系统设计方案,通过无线控制实现不同程序的加载,不需要添加额外的接口与复杂的模块,不需要连接下载线和IDE开发环境等工具,简化了芯片的二次开发,增加了芯片的利用率。并且在FPGA板上测试通过。

引言

随着SoC技术的不断发展,其产品在市场上的占用比例也越来越大。对于SoC的开发流程,它需要有一套相应的IDE开发工具,包括装有配套开发环境的PC、硬件接口和连接线。开发完成后应用于嵌入式领域,但是由于受带开发环境的PC终端、电路板、连接线等条件的约束,一般很难支持二次开发。

为了解决上述技术问题,本文提出一种能方便实现二次开发、芯片利用率高的基于SoC的无线智能程序加载方法。使用带蓝牙功能的终端发送不同的命令即可选择flash程序区中不同的程序加载到内存模块,通过无线控制实现不同程序的加载,不需要添加额外的接口与复杂的模块,不需要连接下载线和IDE开发环境等工具,并提供一种无线智能程序加载SoC系统。经过在FPGA开发板上测试,该方法能很好地应用在智能终端领域中,例如智能玩具小车,主控采用本发明的SoC芯片,就能设定小车的三种工作场景——遥控控制小车、小车自动避障和小车循迹,通过带蓝牙的终端向主控发送相应的命令就能改变小车的工作模式,增加小车的功能。

1 系统总体结构

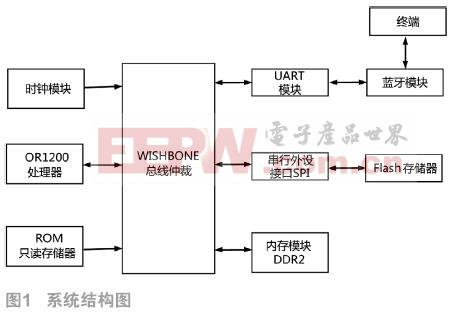

本文中的无线智能程序加载SoC系统包括时钟模块、处理器模块、只读存储器ROM模块、Wishbone总线仲裁模块、SPI控制器模块、内存DDR2模块和通用异步收发传输器UART模块。所有模块均通过Wishbone总线连接到处理器。总线仲裁采用轮循机制实现主设备与从设备之间的访问。本系统改变了传统的把一个程序存储在flash中,当烧录下一个程序时就会覆盖上一个程序的做法,而是把flash划分成三个程序区,烧录flash时,把不同的程序放在不同的程序区。当从SPI flash启动时,程序指针首先指向只读存储器ROM里的bootload区,以完成程序从flash拷贝到内存,再从内存开始执行指令。本系统在此基础上增加了bootload的功能,不仅能完成程序的拷贝,还能监测串口,根据收到的命令选择一个程序区的程序拷贝到内存,使得芯片封装好之后,无需接线,无需相应的IDE软件来加载程序,通过手机或带有蓝牙模块的终端就可以加载不同的程序,简化芯片的二次开发,在智能终端领域能有很好的应用。总体框架图如图1所示。

2 硬件系统设计

2.1 硬件顶层结构设计

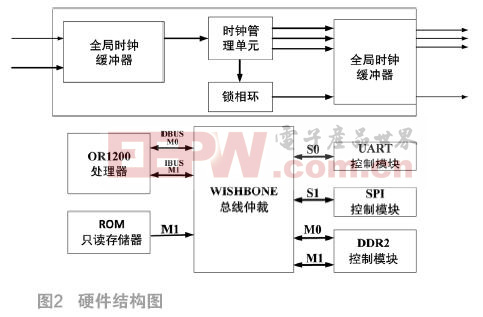

系统硬件顶层采用硬件描述语言Verilog HDL设计,以总线作为分割介质来看整个系统,包括一个主设备和四个从设备。其中主设备为处理器OR1200,从设备为只读存储器模块、内存模块、串行外设接口模块和通用异步手法传输器模块。如图2所示。

2.2 总线仲裁设计

总线仲裁设计主要包含两组仲裁,一组为处理器中的指令总线IBUS,通过高位地址判断从只读存储器ROM取指令还是从内存模块DDR2中取指令;另一组为处理器中的数据总线,通过高八位地址判断访问哪个外设,具体访问哪个寄存器通过低位判断。其中主设备采用轮询的机制抢占总线,核心设计思想为:统计主设备的个数n,然后定义n位的变量token={00....01},通过一定周期把1向左循环取到每个主设备,而实现仲裁的轮循机制。

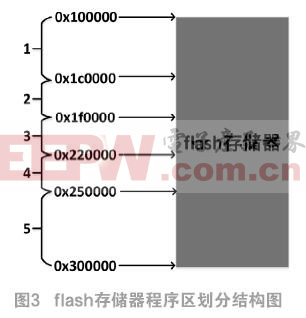

2.3 flash存储器程序区划分结构设计

如图3所示,flash存储器地址从0x100000到0x1c0000是bit文件放置区1,0x1c0001到0x1f0000是程序区Ⅰ2,地址从0x1f0001到0x220000是程序区Ⅱ 3,地址从0x220001到0x250000是程序区Ⅲ4,地址从0x250001到0x300000是扩展区5。SoC系统bit文件利用Xilinx ISE中的impact工具烧录进去,其他程序区的程序通过硬件描述语言中的readmemh命令写入。

3 软件设计

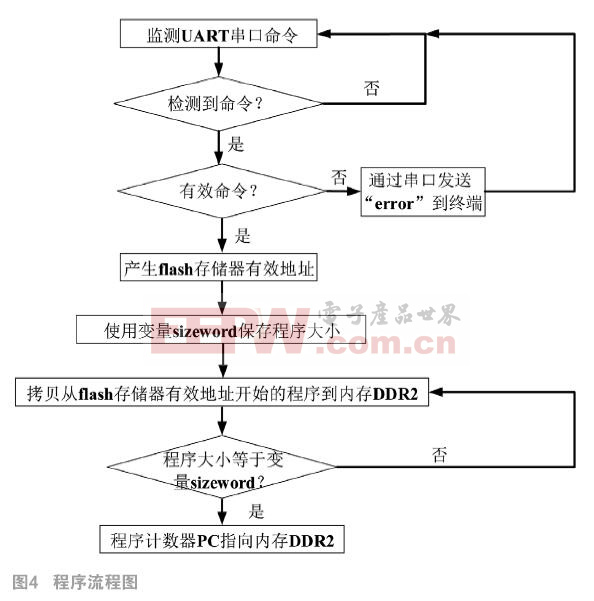

系统在上电启动的时候,程序指针PC指向只读存储器ROM中Bootload区的一段代码,这段代码一般完成程序从flash存储器拷贝到内存,再将程序指针跳转去内存一条一条执行的功能。本文中的软件设计在此基础上增加了改进,如图4所示。首先优化串行外设接口SPI和通用异步收发传输器UART,并实时监测终端发过来的命令;若监测到命令,校验接收到的命令是否为有效命令,若为有效命令则根据接收到的命令选择flash存储器相应程序区的有效地址,否则通过通用异步收发传输器UART和蓝牙模块向终端发送“错误”提示,继续等待命令。得到有效的地址后,初始化串行外设接口SPI,产生串行外设接口SPI时序和发送读命令,根据flash程序区的有效地址拷贝程序到内存模块DDR2中,直到程序大小等于程序大小变量sizeword的值,最后执行跳转命令,将处理器指向内存模块DDR2的起始位置,实现系统的自启动。程序流程图如图4所示。

4 仿真与下板测试

OR1200处理器是OpenRisc家族中的一员,在软件编译的时候我们需要安装OpenRisc交叉编译工具链;采用Xilinx的Virtex-5开发板,同时需要安装ISE等EDA工具。

编译工具链把前面设计的加载启动代码(bootloader)从汇编语言编译成硬件描述语言,并实例化到SoC系统顶层中。然后进行flash存储器的分区并烧录程序,本文通过readmemh命令向程序区Ⅰ、程序区Ⅱ和程序区Ⅲ依次烧录hellowa.c、hellowb.c和hellowc.c。这几个测试程序会通过串口分别打印出“Hello word A”、“Hello word B”和“Hello word C”。这样我们就可以很直观地判断系统在执行哪个程序。

将板子上电,并利用Xilinx ISE中的impact工具将编译好的SoC系统bit文件烧录至flash存储器0x100000到0x1c0000区域,当编译综合通过,下板成功后,我们就可以抓取波形和串口打印判断结果。其波形图和串口打印如图5和图6所示。从波形图中我们可以看出串口控制器输出14个字符,正好是“Hello World A/B/C”,放大波形我们可以看到第一个数据为0x48,正好是字符“H”的ASCLL码。而从窗口上打印的输出更为明显。给串口发送命令“0”,选择flash程序区1 hellowa.c,从0x100000开始拷贝程序,仿真测试结果输出“Hello word A!”。给串口发送命令“1”,选择flash程序区Ⅱ hellowb.c,从0x130001开始拷贝程序,仿真测试结果输出“Hello word B!”。给串口发送命令“2”,选择flash程序区Ⅲ hellowc.c,从0x160001开始拷贝程序,仿真测试结果输出“Hello word C!”。

5 结论

本发明基于SoC的无线智能程序加载方法中,首先将flash存储器划分成若干个程序区,并通过加载指令把不同的程序分别加载到不同的程序区,然后运行加载启动代码,初始化串行外设接口并监测串口接收到的命令,从flash存储器中选择相应程序区,实现程序到内存模块的拷贝,最后执行跳转命令,将处理器指向内存模块的起始位置,实现系统的自启动;整个加载过程简单,不需要接线和留出程序加载接口,也不需要相应的IDE软件来加载程序,通过手机或带有蓝牙模块的终端就可以加载不同的程序,适用范围广。

参考文献:

[1]唐明华,黄诚,刘新,等. 一种基于SoC的无线智能程序加载方法及系统. 国家发明专利. 专利申请号: 201610139229.2. 中国,2015.

[2]苏纪娟,孟祥玲,朱庆明.系统芯片技术国内外发展现状[J]. 军民两用技术与产品. 2015(13).

[3]王龙兴.集成电路的过去、现在和将来(一)世界集成电路的发展历史[J].集成电路应用. 2014(01).

[4]李争,李范鸣,陈捷,等.基于Wishbone SoC总线接口的高性能SDRAM控制器[J].科学技术与工程. 2008(12).

[5]郑文静,李明强,舒继武. Flash存储技术[J]. 计算机研究与发展. 2010(04).

[6]陈光武,范多旺,于超,等.基于Wishbone片上总线的IP核的互联[J].微计算机信息. 2009(20).

本文来源于必威娱乐平台 2017年第9期第54页,欢迎您写论文时引用,并注明出处。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码