基于CCD星载相机图像采集电路设计与实现

0 引言

自从CCD(电荷耦合器件)出现以来,由于其分辨率高、灵敏度高、噪声小、体积小、重量轻、可靠性高等优点,得到了很快的发展,目前已广泛应用于影像传感、卫星监控、空间遥感成像和对地观测等众多领域。对于一个CCD相机系统而言,其核心器件CCD传感器的性能直接影响整个相机系统的性能,而保障其发挥优良的设计难点在于高可靠性的驱动、偏置等与图像采集电路相关的设计,这给设计者带来了很大的麻烦。因此,设计出稳定可靠的CCD图像采集电路是保证CCD传感器乃至CCD相机系统正常发挥其功能的重要条件。

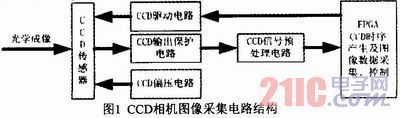

1 CCD相机图像采集电路结构

CCD相机图像采集电路结构如图1所示。CCD传感器接收前端光学系统的成像,偏压电路为CCD传感器提供必需的偏置电压,可编程逻辑器件产生的时序脉冲经过驱动电路对CCD进行控制采集,输出保护电路可对CCD进行有效地防护保护,预处理电路对CCD输出的带噪模拟信号进行处理后便于后续电路使用。

2 CCD传感器的选用

CCD传感器分为面阵CCD传感器和线阵CCD传感器。线阵CCD所需要的驱动时钟较少,驱动电路设计相对简单,面阵CCD所需要的驱动时钟较多,时序较为复杂,驱动电路设计也相对较难。这里我们选择DALSA公司的一款帧转移型面阵CCD1010M,因其具有良好的抗辐射设计,是航空、航天应用中理想的图像传感器,而且其分辨率为1024×1024,还具有良好的抗光晕性能,信号输出噪声低、动态范围大、100%光学填充效率、电荷转移效率高等特点,满足项目需求。它具有的多针相工艺(MPP)还能保证它在低照度下进行工作,通过延长曝光时间来记录非常弱的信号。这款CCD有四相感光区和存储区电极,三相水平读出移位寄存器电极,还有一个输出放大器。输出方式有双路输出和单路输出两种,单通道输出单色逐行扫描图像速度可达30帧/s,并且动态范围大于72dB,性能较为优异。

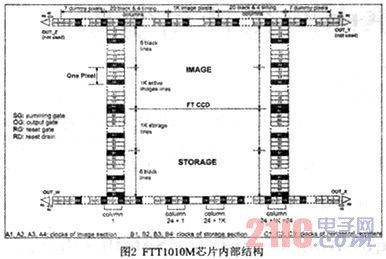

2.1 FTT1010M结构

FTT1010M的内部结构如图2所示。

FTT1010M由感光区和存储区构成,感光区和存储区都由1072H×1030V个像素组成。在感光区中,每个像素单元在垂直方向上可以看作是被四相栅极时钟A1、A2、A3、A4覆盖的相互连接的四个MOS电容器共同组成,它们作为感光区帧转移控制时钟。在1024个有效像素行的上面分别分布着6个黑行(Black Lines),黑行其实就是被遮蔽的不参与光积分的像素行;在水平方向上,每行1072个像素中的有效像素(Active Pixels)为1024个,两边分布着2×20个黑像素(Black Pixels)和2×4个过渡像素(Overscan Pixels),黑像素与黑行一样也是被遮蔽的像素单元,这些单元都不参加光积分,没有光电荷包产生,其主要作用是对CCD的输出视频信号进行预处理时起参考黑电平作用。过渡像素单元的作用主要是在有效像素单元与黑像素单元之间起过渡作用。在存储区中,每个像素单元在垂直方向上可以看作是被四相栅极时钟B1、B2、B3、B4覆盖的相互连接的四个MOS电容器共同组成,它们作为存储区行转移时钟。在存储区水平方向上分布着两个串行输出移位寄存器(Output Register),寄存器内部并没有感光单元,只有用来传输转移感光电荷包的遮蔽的转移单元,每个单元相当于被三相时钟C1、C2、C3覆盖,这些单元都和存储区的像素单元相互衔接对应。其主要作用是将输出放大器连接到水平输出移位寄存器上。

2.2 FTT1010M时序设计

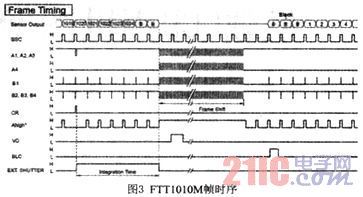

FTT1010M图像传感器的工作时序可以分为帧转移时序(Frame timing),行转移时序(Line timing)和像素读出时序(Pixel timing)。帧转移时序指CCD将一帧图像转移输出的时序,行转移时序指一行像素在时钟的驱动下完成从存储区到水平移位寄存器转移的时序,像素读出时序指在一行像素在C时钟驱动下从水平移位寄存器中逐位水平读出的时序。

FTT1010M的工作过程可分为两个阶段:感光阶段和转移阶段。在感光阶段,图像传感器感光阵列进行电荷积累,存储区进行向水平移位寄存器的电荷转移和水平移位寄存器向输出放大器的电荷输出;在转移阶段,图像传感器主要完成所积累的电荷由感光阵列向存储区的转移。FTT1010M的帧时序如图3所示。

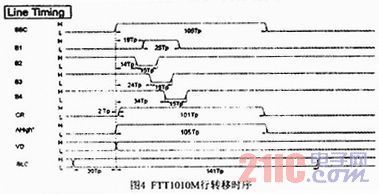

在感光阶段,感光阵列在外界光源的照射下产生电荷,此阶段帧转移控制信号A1、A2、A3、A4不发生变化,感光区和存储区之间为阻断态,电荷不发生转移;而存储区在此阶段处于行转移状态并将电荷进行输出,行转移的过程分为行正程和行逆程两个阶段。在行逆程阶段,SSC为高电平,存储区内各像素单元的电荷在行转移信号B1、B2、B3、B4的控制下向水平移位寄存器方向下移一行,像素转移信号C1、C2、C3不发生变化,图像传感器无像素电荷输出。FTT1010M行转移时序如图4所示。

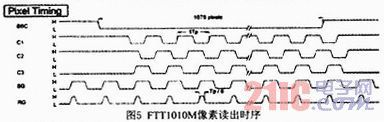

在行正程阶段,SSC为低电平,行转移信号B1、B2、B3、B4不发生变化,水平移位寄存器中的像素电荷在像素转移信号C1、C2、C3的控制下逐次经过输出放大器输出,每输出一行信号后,进行一次行转移。FTT1010M像素读出时序如图5所示。

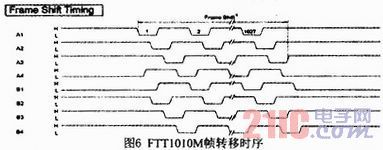

在转移阶段,帧转移控制信号A1、A2、A3、A4与行转移控制信号B1、B2、B3、B4同时作用,交叠变化,将感光区积累的电荷逐行转移到存储区,而在这段时问内像素转移信号C1、C2、C3不起作用,不向外输出电荷。完成整个转移阶段后,又再次进入感光阶段,如此循环往复来保证图像传感器的工作。FTT1010M帧转移时序如图6所示。

3 CCD偏置电压电路

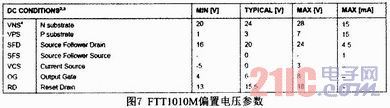

若要使CCD图像传感器芯片正常工作,就需要向CCD提供使其正常工作所需的偏置电压。FTT1010M所需的偏置电压有VNS、VPS、SFD、RD、OG等,它们的参数如图7所示。设计时,作者采用的电压转换方案是使用低纹波的转换芯片搭配转换电路,VNS(24V)由外接28V电压通过DC/DC变换器LT3060得出,SFD由VNS通过电平转换电路得出,VPS、RD与OG由SFD的分压引出。

4 CCD驱动电路

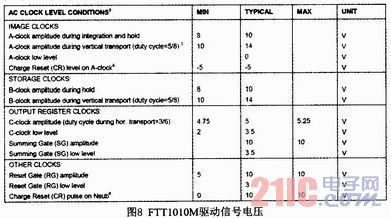

FTT1010M工作时所需的各种脉冲信号的电压如图8所示。

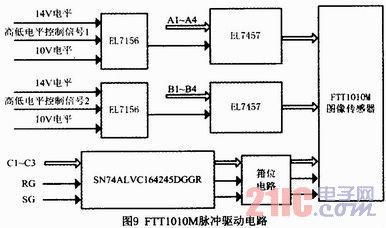

A、B驱动时钟的低位电平为0V,由图8可以看到,在感光阶段,A、B驱动时钟的高位电平为+10V,转移阶段时,A、B驱动时钟的高位电平为+14V。这里我采用EL7156来实现高位电平之间的转换,采用EL7457来实现低位到高位电平的转换。水平读出时钟C需要的低电平不是0V而是3.5V,高电平为8.5V,而FPGA给出的时钟脉冲是低电平为零,高电平为3.3V的脉冲。因此,需要将FPGA产生的时钟通过驱动芯片SN74ALVC164245DGGR进行驱动,使时钟C的幅值达到5V,然后再通过箝位电路的耦合作用来提高脉冲电平,把脉冲提到需要的幅度。SG、RG的产生过程与时钟C的产生过程类似,不同的是其幅值要求为10V。

各种驱动脉冲信号的幅度调整电路如图9所示。

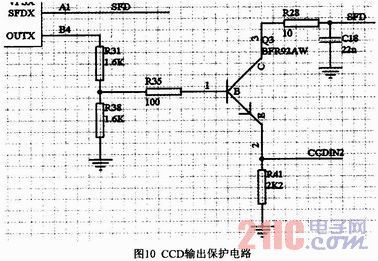

5 CCD输出保护电路

CCD传感器是一种MOS器件,操作不当就很容易受到静电损坏,在电路设计时应在其外围电路加上箝位、限流电路以确保加在CCD上的每一个偏置电压和驱动脉冲受到电流保护,在输入到FTT1010M之前应该通过一个电容来解耦,并且这些解耦电容应该与图像传感器引脚越近越好。FT T1010M的输出端为开源输出,应该在其输出端上接一个电流源做负载,或接一个电阻到地上。在输出上加一个射极跟随的高频三极管,以阻止输出因容性负载而引起的带宽限制。除此以外,射极跟随器加在输出端还可以防止示波器的探头对FTT1010M造成的静电损坏。CCD输出保护电路如图10所示。

6 CCD输出预处理电路

在CCD成像系统中,噪声是限制有效分辨率的最主要因素。CCD输出的信号是具有各种噪声的模拟信号,必须经过预处理,尽可能地消除噪声和各种干扰才能给后续电路使用。为了便于计算机处理,还需要对CCD输出的信号进行A/D转换。预处理过程大体如图11所示。

根据预处理的要求,我们选用了一个高集成度的CCD信号处理专用芯片AD9978,它具有双通道输出能力,且具有14位的A/D转换精度,转换频率可达65MHz,其内部集成了相关双采样、可变增益控制、黑电平箝位电路以及高精度时序产生系统。我们使用相关双采样处理单元,通过两次采样消除不希望的噪声分量,第一次采样位于复位周期结束后,第二次采样位于信号的信息段,两次采样的差就是不含噪声的信号。随后,为了适应不同亮度的目标,防止CCD信号过弱或饱和,我们使用其内的增益控制处理单元来控制信号的增益,最后再通过A/D转换送给后面的可编程逻辑单元进行处理。设计时还要注意使其转换速率与CCD输出像素时钟保持一致。

7 结束语

本文阐述了星载CCD相机图像采集电路的设计与实现,经项目验证表明这些设计能很好地为CCD提供各类偏置电压、驱动脉冲以及电路保护等,它们确保了CCD图像传感器的图像质量,使得CCD相机成像系统具有高性能和高可靠性,具有极高的应用价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码