锂离子电池管理芯片的研究及其低功耗设计 — 数模混合电路的低功耗设计方法(二)

2.2模拟电路的低功耗设计

2.2.1模拟电路低功耗的限制条件

如前所述,在数字电路低功耗设计中,降低电源电压是等比例降低工艺中最常采用也是最有效的办法。但由于实际系统通常采用通用的数字电路工艺,而数字电路优化功耗的方案并没有考虑到对模拟电路功能的影响。对模拟电路而言,电源电压的降低对动态范围(Dynamic Range,DR)和功耗反而不利。

1基本限制条件

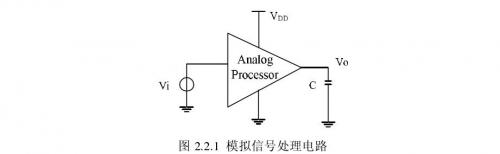

模拟信号电路所消耗的功率是为了维持信号能量超过基本的热噪声,达到给定的信噪比(Signal-to-Noise Ratio,SNR)。图2.2.1给出了一个典型的模拟信号处理电路示意图,它可以是一个放大器、滤波器、振荡器等。电路总的功率为

式中,IDD为流过电源电压V DD的电流,VPP是VDD在电容C端产生的输出电压峰-峰值,ƒ为频率。

式(2.2.1)可知,当VPP接近VDD时,功率将有一个最小值。考虑到信噪比表达式

式中,k为玻尔兹曼常数(1.38×10-23J/K),T为绝对温度。由式(2.2.1)和(2.2.2),可以得到

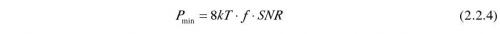

由式(2.2.3)可以看出,在给定的温度下,模拟电路所消耗的功率由电路工作频率(或给定的带宽)、信噪比、电源电压与信号峰-峰值之比所决定。显然,rail-to-rail(即V PP =V DD)电路的功耗最低,为

式(2.2.4)可以看出,在模拟电路中,在信噪比每增加10dB,最小功率的绝对值要增大十倍,而在数字电路中,要实现高信噪比,所牺牲的功耗远远低于模拟电路。还可以看出,式(2.2.4)表示的模拟电路低功耗基本限制条件是一个通用方程,它仅仅给出了功耗与信噪比、速度的关系,而对电压摆幅、电路结构、有源电路产生的噪声没有任何限制条件。对于给定的精度、增益和线性度,设计者总是希望得到一定的动态范围和速度,显然,仅仅用式(2.2.4)无法对不同的方案得出有用的比较结果。因此,设计面向应用的低压低功耗模拟电路之前,必须对实际局限性有较深入的认识,比如噪声和精度。

2实际限制条件

1)与噪声相关的功耗

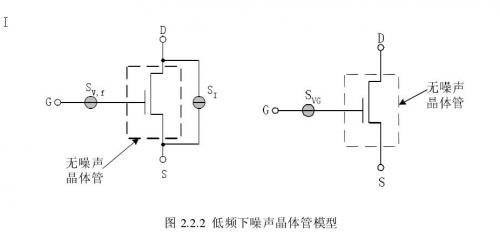

基于噪声对模拟系统的性能有极大的影响,功耗优化必须考虑到电路中器件的噪声。如图2.2.2所示,在低频下,MOS管的噪声模型可分成两个相互独立的随机噪声:一个是热噪声,可用漏源间的电流源表征,另一个是闪烁(或称1/ƒ)噪声,可用与栅极串联的电压源表示。

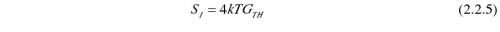

定义热噪声的噪声功率谱密度(Power Spectral Density,PSD)为SI,有

式中,GTH表征晶体管热噪声电导,其大小与MOS管的工作区域有关。通常,可将热噪声电导变换为一个栅极热噪声电阻,即有

式中,gm为器件跨导。

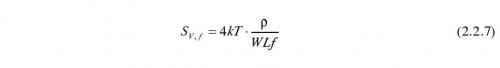

而闪烁噪声的噪声功率谱密度SV,1/ƒ为

式中,ρ在给定的温度下是与工艺相关的常数。

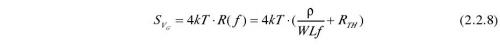

在饱和区,通常可将热噪声和闪烁噪声统一为栅极的总噪声,此时可用一个与频率有关的噪声电阻定义:

结合式(2.2.6)和(2.2.8)可见,在给定的频率下,当跨导增加时,总输入噪声将下降,此时总噪声主要由1/ƒ噪声决定;而增大栅极面积时,总输入相关噪声将主要由热噪声组成。

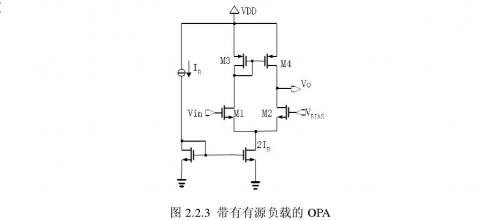

电压信号处理电路中,可以用较常见的运算放大器(OperationalAmplifier,OPA)为例,来讨论噪声对电路功耗的影响。图2.2.3给出了具有有源负载的OPA结构,其中,CL为输出端负载电容。

OPA的增益带宽(Gain Bandwidth,GBW)为

输入电压的噪声功率谱密度为

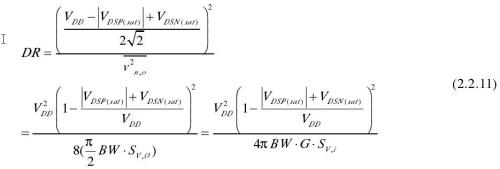

式中,NEF代表过剩噪声因子(Noise Excess Factor, NEF),为了降低噪声,输入对的跨导必须远大于有源负载的跨导,此时NEF接近1.利用噪声带宽的方法可以求得输出噪声功率,在跟随器结构中,增益G=1,则输出端的动态范围DR可以表示为

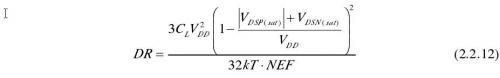

式中 ,分别为PMOS和NMOS的饱和电压。将式(2.2.9)和(2.2.10)代入,则有

,分别为PMOS和NMOS的饱和电压。将式(2.2.9)和(2.2.10)代入,则有

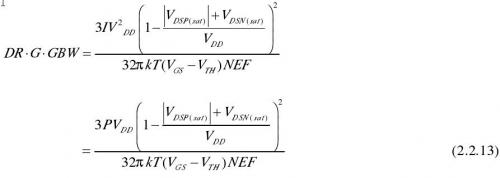

由式(2.2.12)可见,降低电源电压将使输出端的DR急剧下降。当gm =2I/(VGS -VTH)时,由式(2.2.9)和(2.2.12),得

在饱和区,最小的VGS -VTH值为2nUT(其中U T =kT/q为热电压,室温下为26mV,n为亚阈值因子),而且在 时,则由式(2.2.13)可得

时,则由式(2.2.13)可得

式(2.2.14)给出了在给定的动态范围、增益和增益带宽条件下,OPA电路所需要的最小的功耗。它给出了所有重要的设计参数间的约束关系,对电路设计有着重要的指导意义。

2)与精度相关的功耗

模拟电路低功耗设计中,尤其是高速应用场合,必须要考虑精度。而在速度-功耗-精度的约束条件中,最重要的是器件参数的失配。解决失配的方法有失调补偿或是自调零(Auto-zero)技术。但这些补偿技术需要校准过程,在校准期间要中断系统的正常工作,将电路模块的失调电压取样后动态地放在存储器中。这将降低电路工作速度、增加额外的芯片面积以提供校准(Calibration)和复制(replica)电路。在许多高速低功耗电路中,系统通常不允许被中断,或者所需的连续工作时间太长,不能保证失调能及时被纠正。因此,通常认为精度完全是由工艺的匹配性能所决定,典型地,如在高速AD或在DA转换器中,位的精度和晶体管的匹配成正比。

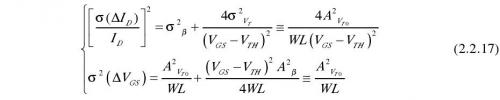

通常,两个理想晶体管间的失配用两个参数来表征,一个是阈值电压失配V T0≡VT01 -VT02,用标准偏差σVT来表示;另一个是电流增益系数β失配△β/β=(β1 -β2)/β,用标准偏差σβ来表示。它们普遍满足下式:

式中,AVT0、Aβ是与工艺相关的常数。

当晶体管为电压偏置时,器件的栅压相同而电流是变量;对于具有相同电流偏置的两个器件(如差分对),电压将相关变化。根据独立的失调分布,可以推出这种相关变化的分布:

MOS管工作在强反型时,式(2.2.16)变为

由式(2.2.17)可以看出,当变量为电流时,增加栅驱动电压可以提高精度。

这也证明了在电流模式电路中,为了达到最佳精度,必须将器件偏置在深饱和区。

与之相反的是,在电压模式电路中,为减小失调电压,必须尽可能地降低Vov的值(令Vov =VGS-VTH),通常可将此值设置在强反型边缘。

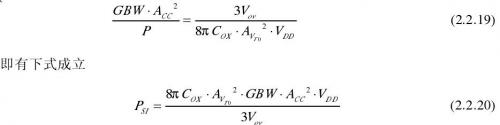

式(2.2.17)还可以看出,要提高电路精度,就需要大尺寸的器件,但与此同时,电路节点的负载电容也增加,为维持给定的速度,就需要更大的功耗。对于单端输入,工作在强反型饱和区的器件,增益带宽由下式决定

对于给定的V ov,定义式(2.2.17)中的电流精度为1/Acurracy2=[σ(△ID)/ID]2,电路所消耗的功率为P=IVDD,则结合式(2.2.18),得到

式(2.2.20)给出的功耗-速度-精度的关系式,它表明在给定的电源电压下,功耗与电路精度的平方成正比,即意味着提高精度和提高速度相比,要付出更大的功耗代价。对于许多更加复杂的电路,如电流信号处理电路、差分对和运放等电压信号处理电路,甚至是多级电路中,式(2.2.20)仍然适用。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码