时间交替ADC系统的实现

由(10)可知时间误差是由于实际采样时钟发生了αk的偏差引起的,由此可以通过时域插值运算对实际采样点t作一个t-αk的时间偏移以达到校正时间误差的目的。

3 实验结果

根据Cyclone III芯片手册可以知道EP3C25Q240C8芯片中FIFO最大支持的时钟频率为238 MHz,同时校正算法中采样频率和信号频率有fs=fo·N/m,因此实际设计中每个ADC采样通道的采样频率为200MSPS,整个系统的采样率最终达到400 MSPS。

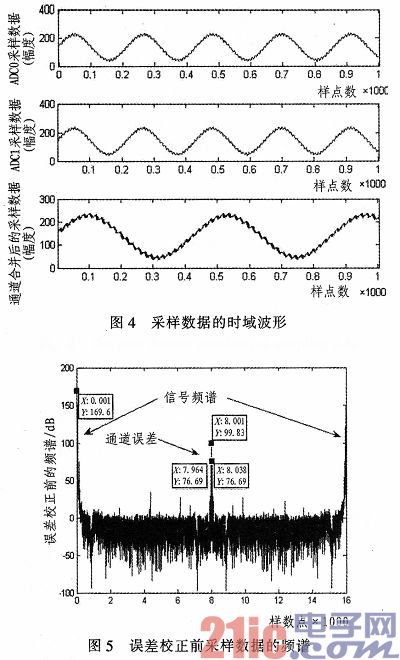

硬件电路设计完成后,在模拟输入端接入幅值为300 mV,频率为1 kHz,偏置和相位都为0的正弦信号作为模拟输入信号,并将FPGA采集到的数据送到Matlab中进行数据分析和误差校正,两个通道每个通道采样点数为8 000个点,下图4中给出了两路采样数据以及两通道采样数据合并后的采样数据(只取了其中100点采样点的局部图),可以看到,最后得到的系统采样数据确实在相同的采样点数内,采样到的数据量为单通道采样的数据量的两倍,达到了提高采样率的目的;同时,采样数据确实存在着一定的误差,这些误差主要是通道间的失配误差造成的。

通过Matlab软件对采集到的数据进行频谱分析和误差校正,可以得到如下图5和6所示的频谱图,图5中所示的是对采集到的数据进行频谱分析,两个通道每个通道采样点数为8 000个点,从图中可以看到得到的3种通误差点基本上是符合前面推断的,同时通道误差的幅度都比较大,严重影响了采样系统的性能;图6中所示的是经过误差算法校正后采样数据的频谱图,可以看到通道误差基本上得到了校正,系统的信噪失真比和无杂散波动态范围都得到了相应的提高。

4 结论

本文利用2片ADC采样芯片及外围电路实现了基于时间交替采样技术的ADC系统,同时分析了这种时间交替采样技术固有的3种通道误差以及对ADC系统的影响;通过Matlab软件分析采样数据,观察这种系统的频谱特性,同时分析通道误差的估算和校正方法,并对实际采样系统系统进行了有效地误差校正;实验证明,通过时间交替采样技术确实可以有效地提高采样频率,同时其通道误差可以根据数学模型进行分析进而得到有效地校正,从而提高系统的性能。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码