短波发射机自动功率控制异常波形采集系统设计

编者按:短波发射机自动功率控制中,算法设计缺陷或反馈控制系统故障可能导致输出波形失真,甚至产生毛刺,损坏发射机功放或降低功放输出效率。针对短波发射机自动功率控制波形检测采集分析中的数据交互量大、实时性要求高等特点,提出了一种自动功率控制异常时波形实时采集设计方案。实验表明,本设计不仅灵活可靠,且能满足大量数据的实时交换要求。

摘要:短波发射机自动功率控制中,算法设计缺陷或反馈控制系统故障可能导致输出波形失真,甚至产生毛刺,损坏发射机功放或降低功放输出效率。针对短波发射机自动功率控制波形检测采集分析中的数据交互量大、实时性要求高等特点,提出了一种自动功率控制异常时波形实时采集设计方案。实验表明,本设计不仅灵活可靠,且能满足大量数据的实时交换要求。

引言

音频信号进入发射机经过调制后,通过信道功率控制使调制信号输出电压值逼近功放理想输入值,从而提高功放效率。信道功率控制主要包括自动增益控制(AGC)与自动电平控制(ALC)。

实际工作中,调制信号经过信道功率控制后会有各种不同的瞬态响应,可能产生毛刺或发生包络失真,从而降低通信质量,增大误码率,严重的可能损坏功放[1]。分析射频信号的毛刺等高频信号的变化特性、功率上升时间、包络长期稳定性等参数,发现射频信号采集分析系统可以检测通信设备功率控制中是否存在设计缺陷或发生故障。这对于保证通信质量和保护功放,具有重要意义。

由于毛刺等高频信号的变化特性往往是瞬态的,因此,对采样检测系统的采样率和处理速度提出了较高要求。此外,由于信号包络变化慢,延续时间长,因此,包络失真检测系统的存储容量足够大。

为实现整个系统功能,需要FPGA和DSP作为下位机,以完成毛刺检测这类“高频”信号特征检测,并可将发现的异常波形标记后返回上位机。另外,由PC完成大存储量、低速的“低频”信号特征(包络失真等)检测。上位机与下位机之间的数据交互量大,实时性要求高,因此,需要一种数据传输更为可靠、传输速率更快的上位机与下位机之间的通信方案。

本文设计了一款可实现上位机与下位机大量数据实时传输的通信系统。下位机由DSP与FPGA构成,完成数字信号的初步处理,其中DSP完成复杂算法及控制任务,FPGA完成实时性要求高、运算量大的毛刺识别等高速信号处理。上位机程序则利用MATLAB编程,完成实时性要求不高但数据量较大的信号处理及显示控制任务。上位机与ARM之间通过以太网连接,基于UDP协议实现。ARM通过HPI接口控制DSP,实现数据采集和命令控制。

1 总体设计

1.1 系统结构

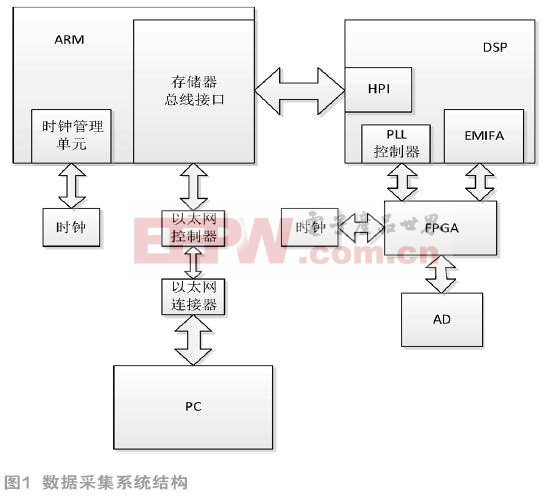

PC机的各类并行总线通常无法直接连接机外高速并口设备,如各类DSP的高速主机接口(HPI,Host Port Interface)。本文采用ARM作为DSP与PC之间的桥梁。PC与ARM之间采用以太网通信方式,ARM与DSP在同一电路板上集成,从而解决了并行高速总线的连接问题,使系统设计简洁,应用方便,同时满足高速数据传输的要求。

图1显示了系统的硬件结构框图。从图1中可以看出,上位机通过网线连接ARM,ARM控制DSP的主机接口,AD采样的大量数据经过FPGA做相应处理后返回给DSP的EMIF接口。数据采集系统中,FPGA与ARM由各自晶振提供时钟,FPGA对晶振频率做锁相处理后给DSP和A/D提供时钟。

系统中,ARM控制板基于TI公司的LM3S9B96芯片;FPGA采用ALTERA公司StratixⅡ系列的EP2SGX30D;DSP选用了TI公司的TMS320C6416。

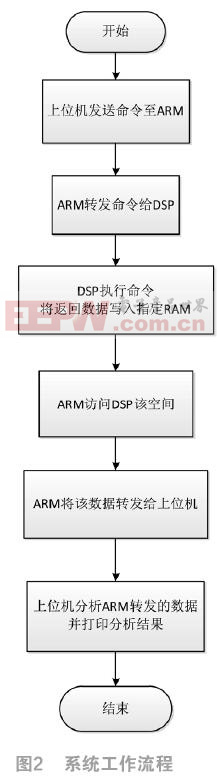

1.2 工作流程

上位机与DSP完成一次通信的工作流程如图2所示。从上位机发出的命令被处理成UDP报文形式后,经过以太网连接器与控制器进入ARM,再经过UDP协议解析后被转发送至DSP。由于ARM直接控制HPI接口,因此,命令转发过程即是ARM改写DSP的RAM空间的过程。DSP收到命令后将解析报文,执行命令。执行完命令后,DSP将要返回给上位机的数据写到之前定义好的RAM空间内。ARM之后将访问DSP的RAM空间,即进行读操作,将该数据整理成UDP报文形式,并通过网口转发给上位机。DSP与ARM之间采用中断方式通知对方新数据或命令的到来。

2 硬件设计

2.1 ARM控制板设计

ARM开发板硬件设计如图3所示。本设计中的ARM开发板是基于TI公司的LM3S9B96芯片,其硬件模块主要包括1个看门狗复位电路、1个网络变压器以及2个晶体振荡器。

LM3S9B96的时钟来源是主振荡器(MOSC)或16MHz内部振荡器(IOSC)。最终产生的系统时钟用于Cortex-M3处理器内核以及大多数片内外设。本设计中,主振荡器通过外部单端时钟源连接到OSC0输入引脚,以提供频率精准的时钟源。

看门狗复位电路是一个定时器电路。正常工作的MCU每隔一段时间输出一个复位信号到看门狗复位电路输入端,给WDT清零。若超过规定时间未发送复位信号(一般在程序陷入死循环时),WDT定时超过后,看门狗电路就会发出一个复位信号到MCU,使MCU复位,防止MCU死机[2]。

LM3S9B96芯片集成了MAC和PHY功能,只需要连接集成变压器的RJ45网口和必要的阻容器件,便可以实现以太网通信。

2.2 DSP主机接口(HPI)设计

上位机通过ARM可访问主机接口(HPI)。主机接口是主设备或主处理器与DSP的通信接口。在C6x系列DSP中,主机接口是一个16位或者32位宽的并行端口,可以实现并行高速数据传输[3]。上位机掌管该接口的控制权。通过上位机不仅可以直接访问DSP所有的存储空间,而且可以直接访问DSP片内存储空间映射的外围设备。

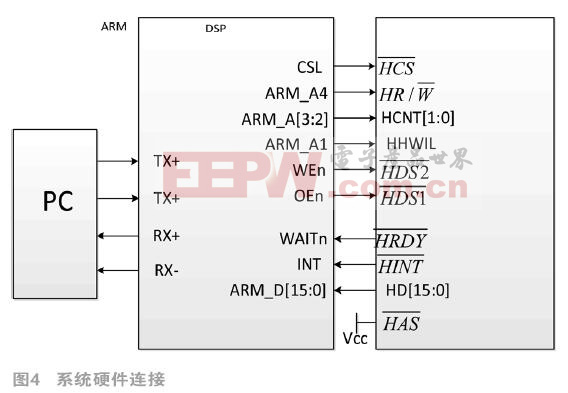

系统硬件连接如图4所示。本设计中,ARM的地址线AMR_A[4:1]复用为HPI接口的控制信号。HCNTL[1:0]用作接口功能选择,用来区分外部主机当前访问的HPI寄存器种类[4]。

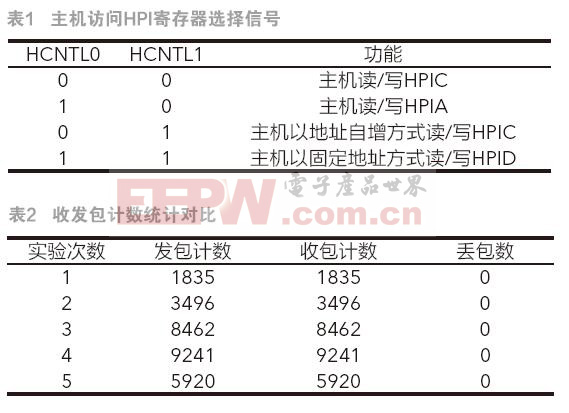

表1描述了主机访问HPI寄存器的选择信号HCNTL[1:0]。HR/W信号决定当前对HPI接口是读或写的操作。内部HPI选通信号来源于3个输入信号HCS、HDS1和HDS2。HCS输入用于使能HPI、HDS1和HDS2信号控制着HPI的数据传输。通过这些信号控制线可以顺利实现HPI的读/写操作。

上位机通过网口与ARM开发板连接,信号均为差分输入,差分输出。

2.3 射频信号采集

射频信号采集采用ADI公司的AD9637实现。AD9637可同步将8路模拟射频信号转换为数字信号,转换精度有10bit与12bit可选,转换速率最高可达80MSPS,最大数据量为480MSPS,用户可通过芯片的SPI控制口对AD9637进行设置。

本设计中,DSP通过FPGA实现SPI接口与AD9637通信。考虑到实际采样信号为2M~30M的短波射频信号,设置AD采样时钟为62.5MHz,并使用斩波(CHOP)模式,从而使其具有较小的低频分量。

3 软件设计

3.1 基于MATLAB的上位机软件设计

上位机程序基于MATLAB R2012a开发。利用MATLAB图形用户接口开发环境(GUIDE)可以方便地建立GUI对象,同时建立M文件框架。用户在该框架下编写GUI组件的回调函数,可以控制并决定GUI对用户操作的响应。

本设计中,DSP负责实时高速采样的分析。DSP将采样数据发送至上位机,MATLAB负责大量非实时低速信号的分析。上位机与ARM之间的通信基于UDP协议,即用户数据报协议。UDP协议提供面向事务的简单不可靠信息传送服务,属于传输层协议。虽然UDP不提供数据包分组、组装,不能对数据包进行排序,在网络环境较差的情况下存在丢包问题,但其有简单、高效的优点。在本设计中,PC与ARM通过网线连接,传输距离不远,网络质量较好,不必考虑丢包问题。

UDP报文一般分为首部和数据区两部分。本设计中,首部内容包括源端口、目的端口、报文长度与校验和[5]。MATLAB软件提供了UDP对象的创建函数。本设计在此基础上设计了顶层协议,并根据协议编写了数据读取程序,将读取到的数据打印或存入工作空间,进行包络失真等检测[6]。

在上位机给DSP下达命令前,需要对发送端与接收端的参数进行设置。参数设置包括本地IP地址、本地发送端与接收端端口号、远端IP地址、远端数据发送端和接收端的端口号。基本参数设置完毕后,将设置接收端缓存大小。然后,打开接收数据端UDP,在后台等待下位机数据。

上位机发送命令时,预先设置发送数据端缓存大小;打开发送数据端UDP后,发送命令;数据发送完成后,关闭发送数据端UDP。

3.2 下位机软件设计

3.2.1 ARM控制板软件设计

本设计中,ARM主要负责上位机与DSP之间的通信,以Keil uVision4作为开发环境,C++语言为开发语言。

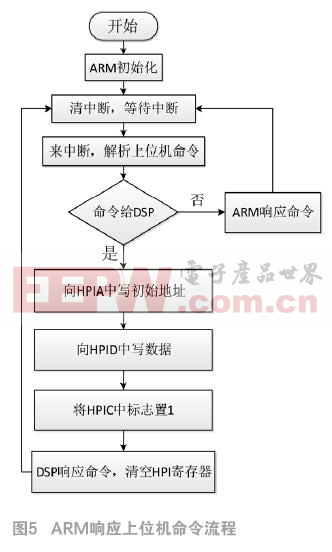

在实现上位机与DSP通信前,ARM先进行初始化。初始化过程包括设置系统时钟、EPI总线初始化、设置本地IP、目标IP及物理地址等参数,设置回调函数响应中断、定时器初始化以及清中断。设计中定义的回调函数包括ARM向DSP转发命令函数与ARM向上位机转发数据函数。定义完回调函数后,回调函数的函数指针会注册给调用者。当收到来自上位机或DSP的中断后,ARM将使用函数指针调用指定的回调函数对事件进行处理[7]。

初始化完成后,ARM的IP地址、HPI接口控制寄存器、地址寄存器的初始值均设置完毕,开始等待上位机发来的命令,即等待中断的过程。DSP返回数据给ARM前,同样也会给ARM硬中断,从而通知ARM对DSP进行读操作。当收到来自上位机或DSP的中断后,ARM会根据特定中断调用事先定义好的回调函数,实现命令或数据的透传[8]。

3.2.2 DSP主机接口控制软件设计

HPI接口通过EDMA控制器与内存空间相连,因此,上位机访问DSP内存空间时不需要DSP的CPU参与。主机通过操作3种不同的HPI寄存器实现对DSP内存的访问,分别为控制寄存器(HPIC)、地址寄存器(HPIA)和数据寄存器(HPID)[9]。

中断后,ARM将执行之前定义好的回调函数,接收UDP报文并解析。上位机既可以通过网口给ARM发送命令,也可给DSP发送命令。ARM收到来自上位机的中断后,会先将命令解析,分析是否是给自己的命令。若是,则将命令透传给DSP。ARM透传命令给DSP时,将访问DSP的RAM地址,命令内容写入相应寄存器,并改写控制寄存器,通知DSP访问该空间并执行命令。DSP执行完命令后,将数据写入之前定义好的RAM内,拉低HINT,通知ARM访问该空间并将数据转发给上位机。ARM收到上位机命令后的工作流程如图5所示。

4 实验验证

本文通过对下位机数据发送包计数与上位机数据接收包计数进行统计对比,得出此通信方案的可靠性。经过多次实验对比,部分收发数据包计数统计如表2所示。可见,上位机收包计数与下位机发包计数结果基本一致,说明本通信设计方案可靠性高,且满足大量数据实时交换的要求。

5 结语

本文设计并实现了一种以ARM为桥梁实现上位机与DSP通信的嵌入式系统,给出了系统设计总框图,介绍了ARM与DSP通信接口设计、上位机程序设计以及系统开始工作后信号在系统中的处理及流程。本文设计的通信结构高速、稳定且易于调试,可推广应用到各种信号采集和控制系统的设计中。

参考文献:

[1]赵俭,张效义,于永莉.突发通信模式下数字自动增益控制的FPGA实现[J].舰船科学技术,2006,28(03):53-55.

[2]孙雪飞,胡巍.例说TI ARM Cortex-M3--基于LM3S9B96[M].北京:北京航空航天大学出版社,2013.

[3]汪安民,张松灿,常春藤.TMS320C6000 DSP实用技术与开发案例[M].北京:人民邮电出版社,2008.

[4]熊斌,赵曙光,郭星明.一种多路视频处理系统新方案[J].通信技术,2011,44(05):116-118.

[5]蔡钧,段文伟,付俊杰等.一种改进的DCS通信接口方案及应用[J].自动化仪表,2011,32(08):50-52.

[6]Chia-han Y,Gulnara Z,Yang Chen-Wei,et al.Cosimulation Environment for Event-Driven Distributed Controls of Smart Grid[J].IEEE Transactions on Industrial Informatics,2013,9(03):1423-1435.

[7]裴科,张刚.一种互补性多处理器系统中OS间通信接口设计[J].计算机工程与应用,2010,46(17):60-62.

[8]曹理发.基于ARM+DSP的视频处理系统设计与实现[D].武汉:武汉理工大学,2008.

[9]吴剑剑.一种基于ARM+FPGA+DSP嵌入式实时图像处理平台设计与实施[D].武汉:华中科技大学,2012.

本文来源于中国科技期刊必威娱乐平台 2016年第8期第38页,欢迎您写论文时引用,并注明出处。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码