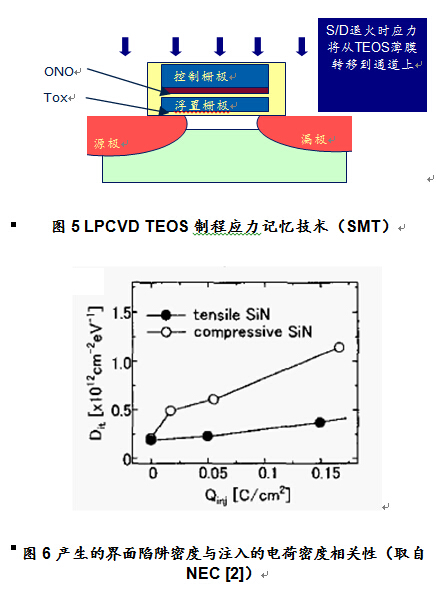

LPCVD TEOS 厚度的机械应力对闪存循环性能的影响

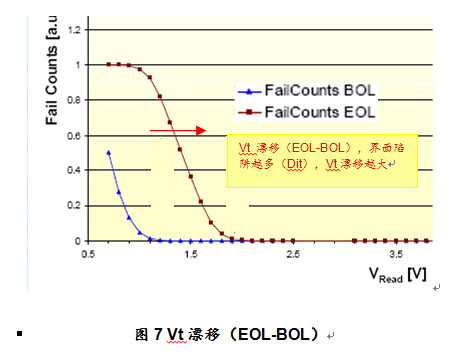

从实验中可知,由于通过减小LPCVD TEOS厚度改进循环Vt漂移对PCM、fLWR及良品率无负面影响,LPCVD TEOS目标厚度即于2009年12月份从12.5nm改成11.5nm。

结论

为了保证最终用户能获得高度可靠的NVM(非易失性存储器),改进循环(耐久性)性能极其重要。本研究得出了一个非常有趣的结论:LPCVD TEOS厚度可影响闪存循环Vt漂移。将TEOS厚度从12.5nm降至11.5nm,有助于在700k的P/E循环之前针对读取失败获取更多制程裕度:TEOS厚度减小1nm,制程裕度增大约20mV。

工作展望

从多个DOE批次的实验中可知,NVM循环性能可能受到许多制程的影响,包括HTN RF功率、FSI清洗速度、RTP侧壁氧化厚度、IMD配方、以及LPCVD TEOS厚度。而且,如图8所示,在SCTEOS厚度降至11.5nm后,循环Vt所受的影响并不明显,这和我们在3个DOE批次被分别实验的图3b中看到的一样。这表明,除LPCVD TEOS厚度外,还有其他制程也会影响Vt漂移。然而,如今我们还未完全弄清楚影响Vt漂移的决定性因素。因此,弄明白可以优化NVM P/E循环性能同时不影响其他电学参数的方法及工艺窗口很重要。循环失败的根本原因探索之旅仍在继续。为了在循环性能上获取更多制程裕度,我们同时开展了许多工作。

此外,借助透射式电子显微镜(TEM)利用会聚束电子衍射(CBED)测量闪存单元中的局部应力这一内部方法,对于以后的研究也很有用。

参考文献

[1] Victor Chan, Ken Rim, Meikei Ieong, Sam Yang, Rajeev Malik, Young Way Teh, Min Yang, Qiqing (Christine) Ouyang, Strain for CMOS performance Improvement - IBM Systems & Technology Group, IBM Research Division, T. J. Watson Research Center and ; Chartered Semiconductor Mfg. Ltd

[2] Akio Toda, Shinji Fujieda, Kohji Kanamori, Junichi Suzuki, Kammasa Kuroyanagi, Noriaki Kodama, Yasuhide Den, and Teiichiro Nishizaka; IMPACT OF MECHANICAL STRESS ON INTERFACE TRAP GENERATION FLASH EEPROMs; System Devices Research Laboratories, NEC Corporation, I I20 Shimokuzawa, Sagamihara, Kanagawa 229-1 189, Japan System Memory Division and Process Technology Division, NEC Electronics Corporation, 1 120 Shimokuzawa, Sagamihara, Kanagawa

[3] Scott E. Thompson, Member, IEEE, Mark Armstrong, Chis Auth, Mohsen Alavi, Mark Buehler, Robert Chau, Steve Cea, Tahir Ghani, Glenn Glass, Thomas Hoffman, Chia-Hong Jan, Chis Kenyon, Jason Klaus, Kelly Kuhn, Zhiyong Ma, Brian Mcintyre, Kaizad Mistry, Member, IEEE, Anand Murthy, Borna Obradovic, Ramune Nagisetty, Phi Nguyen, Sam Sivakumar, Reaz Shaheed, Lucian Shifren, Bruce Tufts, Sunit Tyagi,Mark Bohr, Senior Member, IEEE, and Youssef El-Mansy, Fellow, IEEE, A 90-nm Logic Technology Featuring Strained-Silicon

[4] Bhadrii Varadarajja, Jiim Siims PECVD Busiiness Uniitt Novellllus Systtems, IInc.., High Stress Silicon Nitride Films for Strained Silicon Technology

[5] Ming-Shing CHEN, Yean-Kuen FANG, Tung-Hsing LEE, Chien-Ting LIN, Yen-Ting CHIANG, Joe KO1, Yau Kae SHEU1, Tsong Lin SHEN1, and Wen Yi LIAO1, Effect of Etch Stop Layer Stress on Negative Bias Temperature Instability of Deep Submicron p-Type Metal–Oxide–Semiconductor Field Effect Transistors with Dual Gate Oxide

[6] In-Shik Han, Student Member, IEEE, Hee-Hwan Ji, Ook-Sang You, Won-Ho Choi, Jung-Eun Lim, New Observation of Mobility and Reliability Dependence on Mechanical Film Stress in

Strained Silicon CMOSFETs

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码