TMS320C6678存储器访问性能(上)

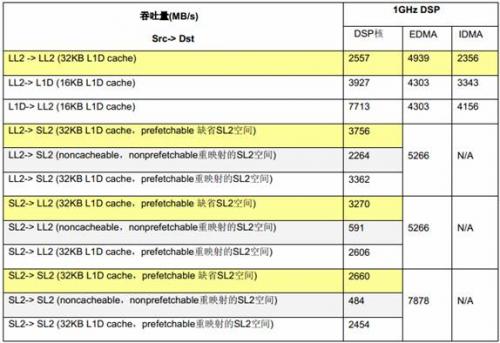

表3 列出了在1GHz C6678 EVM(64-bit 1333MTS DDR)上,在不同情况下用EDMA,IDMA和DSP核做大块连续数据拷贝测得的吞吐量。

在这些测试中,L1上的测试数据块的大小是8KB;IDMA LL2->LL2 拷贝的数据块的大小是32KB;其它DSP核拷贝测试的数据块的大小是64KB,其它EDMA拷贝测试的数据块大小是128KB。

吞吐量由拷贝的数据量除以消耗的时间得到。

表3 DSP核,EDMA和IDMA数据拷贝的吞吐量比较

总的来说,DSP核可以高效地访问内部存储器,而用DSP 核访问外部存储器则不是有效利用资源的方式;IDMA非常适用于DSP核本地存储器 (L1D,L1P,LL2) 内连续数据块的传输,但它不能访问共享存储器(SL2, DDR) ;而外部存储器的访问则应尽量使用EDMA。

Cache配置显著地影响DSP核的访问性能,Prefetch buffer也能提高读访问的效率,但它们不影响EDMA和IDMA。这里所有DSP核的测试都是基于cold cache(cache 和Prefetch buffer在测试前被清空)。

对DSP核,SL2可以通过从0x0C000000开始的缺省地址空间被访问,通常这个地址空间被设置为cacheable 而且prefetchable。SL2可以通过XMC(eXtended Memory Controller) 被重映射到其它存储器空间,通常重映射空间被用作non-cacheable, nonprefetchable访问(当然它也可以被设置为cacheable 而且prefetchable)。通过缺省地址空间访问比通过重映射空间访问稍微快一点。

前面列出的EDMA 吞吐量数据是在EDMA CC0(Channel Controller 0) TC0(Transfer Controller 0)上测得的,EDMA CC1和EDMA CC2的吞吐量比EDMA CC0低一些,后面有专门的章节来比较10个EDMA传输控制器的差别。

3. DSP核访问存储器的时延

L1和DSP核的速度相同,所以DSP核每个时钟周期可以访问L1存储器一次。对一些特殊应用,需要非常快的访问小块数据,可以把L1的一部分配置成普通RAM(而不是cache)来存放数据。

通常,L1被全部配置成cache,如果cache访问命中(hit),DSP核可在一个周期完成访问;如果cache访问没有命中(miss),DSP核需要等待数据从下一级存储器中被读到cache中。

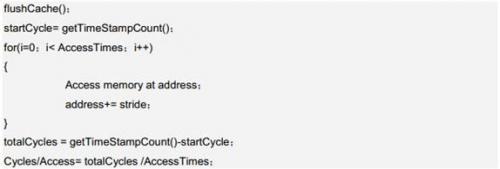

本节讨论DSP核访问内部存储器和外部DDR存储器的时延。下面是时延测试的伪代码:

3.1 DSP核访问LL2的时延

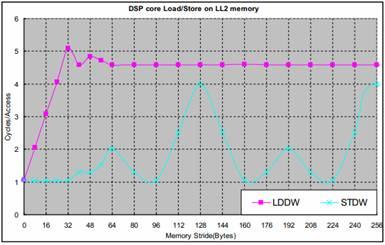

图2是在1GHz C6678 EVM上测得的DSP核访问LL2的时延。DSP核执行512个连续的LDDW(LoaD Double Word) 或STDW(STore Double Word) 指令所花的时间被测量,平均下来每个操作所花的时间被画在图中。这个测试使用了32KB L1D cache。

图2 DSP核访问LL2

对LDB/STB和LDW/STW的测试表明,它们的时延与LDDW/STDW相同。

由于L1D cache只有在读操作时才会被分配,DSP核读LL2总是通过L1D cache。所以,DSP核访问LL2的性能高度依赖cache。多个访问之间的地址偏移(stride)显著地影响访问效率,地址连续的访问可以充分地利用cache;大于或等于64字节的地址偏移导致每次访问都miss L1 cache因为L1D cache行大小是64 bytes。

由于L1D cache不会在写操作时被分配,并且这里的测试之前cache都被清空了,所以任何对LL2的写操作都通过L1D write buffer(4x16bytes)。对多个写操作,如果地址偏移小于16bytes,这些操作可能在write buffer中被合并成一个对LL2的写操作,从而获得接近平均每个写操作用1个时钟周期的效率。

当多个写操作之间的偏移是128bytes整数倍时,每个写操作都访问LL2的相同sub-bank(LL2包含两个banks,每个bank包含4个总线宽度为16-byte的sub-bank),对相同sub-bank的连续访问的时延是4个时钟周期。对其它的访问偏移量,连续的写操作会访问LL2不同的bank,这样的多个访问的在流水线上可以被重叠起来,从而使平均的访问时延比较小。

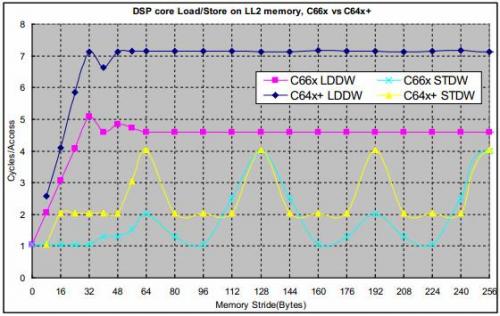

C66x核在C64x+核的基础上有很多改进,C66x核的L2存储器控制器和DSP核速度相同,而C64x+的L2存储器控制器的运行速度是DSP核速度的1/2。图3比较了C66x和C64x+Load/Store LL2存储器的性能

图3 C66x和C64x+核在LL2上Load/Store的时延比较

3.2 DSP核访问SL2的时延

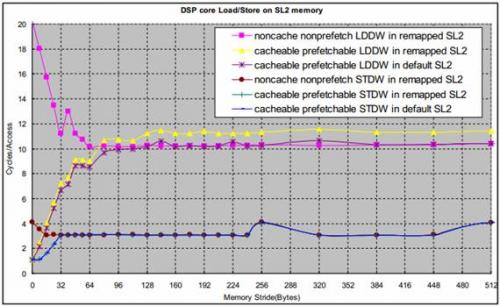

图4 是在1GHz C6678 EVM上测得的DSP核访问SL2的时延。DSP核执行512个连续的LDDW(LoaD Double Word) 或STDW(STore Double Word)指令所花的时间被测量,平均下来每个操作所花的时间被画在图中。测试中,L1D被配置成32KB cache。

图4 DSP核访问SL2

对LDB/STB和LDW/STW的测试表明,它们的时延LDDW/STDW相同。

关键词: TMS320C6678 存储器

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码