Tcl在Vivado中的应用

Tcl 语言的基本语法相对简单,但要熟练掌握仍需日常不断练习。 Xilinx 网站上有很多相关资料,这里推荐两个跟 Tcl 相关的文档 UG835 和 UG894 , 希望对大家学习 Vivado和 Tcl 有所帮助。

2 在Vivado中使用Tcl定位目标

在 Vivado 中使用 Tcl 最基本的场景就是对网表上的目标进行遍历、 查找和定位,这也是对网表上的目标进行约束的基础。要掌握这些则首先需要理解 Vivado 对目标的分类。

2.1 目标的定义和定位

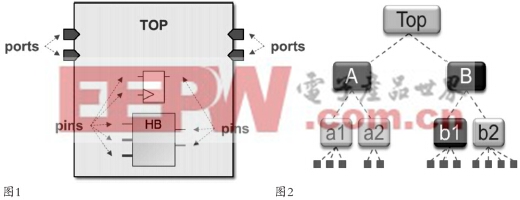

如图1所示,设计顶层的 I/O 称作 ports,其余底层模块或是门级网表上的元件端口都称作 pins。而包括顶层在内的各级模块、 blackbox 以及门级元件,都称作 cells。连线称作 nets,加上 XDC 中定义的 clocks,在 Vivado 中一共将网表文件中的目标定义为五类。要选取这五类目标,则需用相应的 get_*命令,例如 get_pins 等等。

get_ports

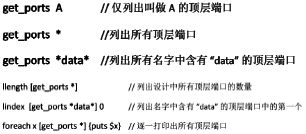

ports 仅指顶层端口,所以 get_ports 的使用相对简单,可以配合通配符“* ” 以及 Tcl语言中处理 list的命令一起使用。如下所示。

get_cells/get_nets

不同于 ports 仅指顶层端口,要定位 cells 和 nets 则相对复杂,首先需要面对层次的问题。这里有个大背景需要明确: Vivado 中 Tcl/XDC 对网表中目标的搜索是层次化的,也就是一次仅搜索一个指定的层次 current_instance,缺省值为顶层。

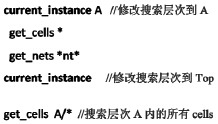

以图2所示设计来举例, 若要搜索 A(不含 a1,a2) 层次内的所有 cells 和名字中含有 nt 的 nets, 有两种方法:

若要将搜索层次改为 A+B+b1,则可以写一个循环, 逐一用 current_instance 将搜索层次指向 A, B 和 b1,再将搜索到的 cells 或 nets 合成一个 list 输出即可。

若要将搜索层次改为当前层次以及其下所有子层次, 可以使用 -hierarchical (在 Tcl中可以简写为-hier )。

在使用-hierarchical 时有一点需要特别留意,即后面所跟的搜索条件仅指目标对象的名字,不能含有代表层次的“ /” 。 下面列出的写法便是一种常见的使用误区, 并不能以此搜索到 A 及其下子层次内所有的 cells。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码