降低工业应用的总体拥有成本

编者按: 摘要:大约三分之一的嵌入式设计人员考虑在嵌入式应用中采用FPGA,他们认为在设计中使用FPGA过于昂贵。但是,从系统级了解总体拥有成本(TCO) (由产品生命周期中的开发、改进、替换和维护成本来衡量),您会发现FPGA是分立微控制器(MCU)/数字信号处理器(DSP)/ASSP产品灵活的竞争方案。 引言 工业自动化和过程控制生产商一直面临持续的全球竞争和经济压力,商业模式和利润不断受到威胁,不得不应对成本挑战,包括: ● 利润和研发投入; ● 产品及时面市压力以适应经济状况的变

对于硬件设计人员,具有嵌入式处理器的FPGA器件的优势是非常明显的。很多操作系统公司提供全面支持,对功能进行改进,因此,很多软件工程师开始采用基于FPGA的系统,发挥其优势,延长产品生命周期。硬件和软件工程师需要进行一定的投入来学习C程序软件编程和FPGA设计的VHDL编程。但是,一旦设计人员决定采用FPGA设计方法,FPGA比仅采用MCU和DSP器件的解决方案性价比更高,更灵活。

对多个设计进行修改

以本文使用驱动为例,如果从这一基本平台开发的y产品具有不同的特性,那么,设计团队必须首先在每块电路板的x器件上实现其硬件和软件,花费t时间,然后,对这些产品例化硬件和软件y次,花费t2时间来完成多个产品。这带来的成本因素是((x × t) × (y × t2))。设计团队已经知道这一方法并不简单,产品无法迅速面市,不能降低包括开发、改进、支持、维护和替换成本等在内的产品生命周期成本。

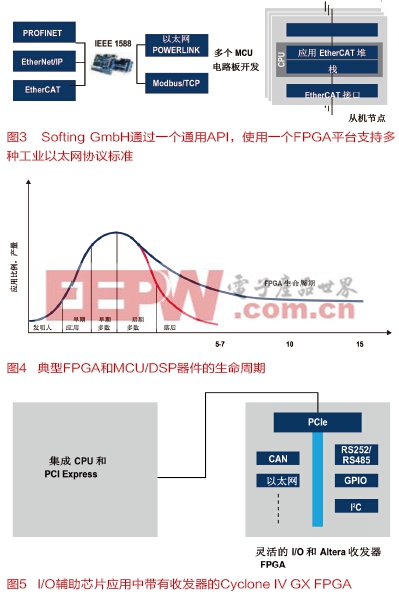

为简化这一过程,设计人员可以利用Cyclone系列体系结构,设计支持多条产品线(SKU)和多种功能的通用硬件平台(如图3)。在最初设计基础上,对于每一后续产品,基于FPGA的产品支持工程师重新配置Cyclone系列FPGA,不需要重制PCB(印制板),节省了设计团队数月的工程工作时间。

考虑驱动生产商提供支持多种网络协议的产品这一实例,例如EtherCAT、PROFINET (RT/IRT)和Modbus/TCP等。MCU/DSP解决方案不仅需要额外的器件来支持通信通道,而且还需要三块电路板。对于设计人员,开发或者许可协议专用MAC IP (如果需要)和协议专用堆栈,三块电路板的成本会高达$300K (每块电路板$100K),而且还要考虑相应的软件开发成本。

但是,设计人员可以使用Cyclone或者MAX 10 FPGA,在相同的FPGA上集成驱动控制和工业以太网,使用相同的硬件平台支持多条产品线(SKU)和所需要的功能。在前面提到的实例中,不需要开发三块电路板(每一IE协议标准一块),供应商在产品中使用很少的元器件和PCB,节省了$150K到$200K的MCU/DSP开发成本,显著降低了BOM成本。由于减少了PCB电路板设计,生产商也简化了与产品存储和运输相关的物流过程。考虑到所有开发资源和时间因素后,FPGA设计方法有助于工程师克服((x × t) × (y × t2))成本问题。

当设计发挥了FPGA器件的最大能力后,设计人员可以将设计移植到高密度器件或者重新编译设计,迅速采用其他的Altera FPGA。从另一角度看,这还是一种快速更新方法,使设计人员能够集成功能,在电路板上减少甚至不采用MCU、DSP和其他元器件。

发挥较长生命周期的优势

产品可靠性有利于降低长期TCO。而且,与Altera FPGA相比,很多MCU和DSP器件的生命周期要短得多,通常在5到7年范围内,这是因为它们的供应商会比Altera更快停止供应成熟器件,如图4所示。Altera的策略是支持较长的产品生命周期,一般能够达到15年。

处理器的支持

对于出于性能原因而需要外部主机处理器的应用,设计人员可以采用主流体系结构,例如,Intel® ATOM™处理器和其他基于PCI Express® (PCIe®)的处理器。设计人员可以利用这类处理器体系结构强大的软件回显系统。他们还可以使用这些处理器提供的高速PCIe接口,与I/O辅助芯片进行通信,集成外设和I/O阵列,支持各种工业以太网协议、SATA和其他IP。图5所示为灵活的Altera FPGA I/O辅助芯片体系结构。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码