解析FPGA低功耗设计

下面介绍一下优化BRAM功耗的方法:

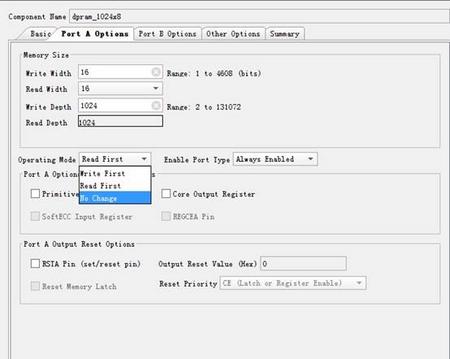

a)使用“NO CHANGE”模式:在BRAM配置成True Dual Port时,需要选择端口的操作模式:“Write First”,“Read First” or “NO CHANGE”,避免读操作和写操作产生冲突,如图6所示;其中“NO CHANGE”表示BRAM不添加额外的逻辑防止读写冲突,因此能减少功耗,但是设计者需要保证程序运行时不会发生读写冲突。

图6

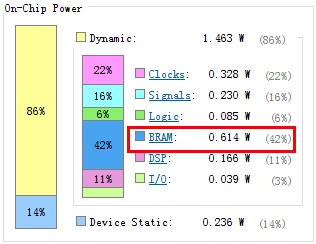

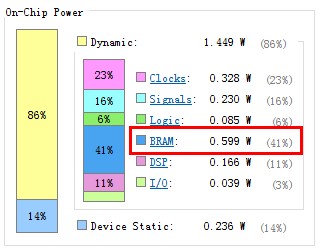

图5中的功耗是设置成“Write First”时的,图7中是设置成“NO CHANGE”后的功耗,BRAM的功耗从0.614W降到了0.599W,因为只使用了7%的BRAM,如果设计中使用了大量的BRAM,效果能更加明显。

图7

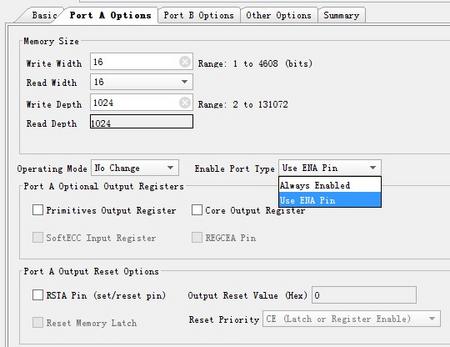

b)控制“EN”信号:BRAM的端口中有clock enable信号,如图8所示,在端口设置中可以将其使能,模块例化时将其与读/写信号连接在一起,如此优化可以使BRAM在没有读/写操作时停止工作,节省不必要的功耗。

图8

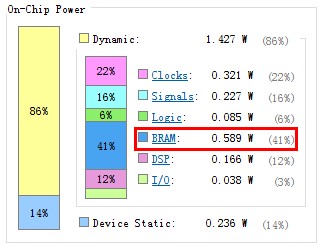

如图9所示为控制“EN”信号优化后的功耗情况,BRAM功耗降到了0.589W。

图9

c)拼深度:当设计中使用了大量的存储器时,需要多块BRAM拼接而成,如需要深度32K,宽度32-bit,32K*32Bit的存储量,但是单块BRAM如何配置是个问题?7 series FPGA中是36Kb 的BRAM,其中一般使用32Kb容量,因此可以配置成32K*1-bit或者1K*32-bit,多块BRAM拼接时,前者是“拼宽度”(见图10),后者是“拼深度”(见图11)。两种结构在工作时,“拼宽度”结构所有的BRAM需要同时进行读写操作;而“拼深度”结构只需要其中一块BRAM进行读写,因此在需要低功耗的情况下采用“拼深度”结构。

注:“拼深度”结构需要额外的数据选择逻辑,增加了逻辑层数,为了降低功耗即牺牲了面积又牺牲了性能。

图10

图11

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码