一种于FPGA的多通道频率测量系统设计

3)对过滤后的真实被测频率信号fre_real1进行上升沿判断,以确定频率计数的起始与结束,控制频率计数器的计数与输出过程。

4)计数值输出过程中,需设置count_delay来判断频率信号的周期是否大于1s,如果成立,则认定外部无频率信号输入,输出值置为NAN(表示无穷大)。同时,系统启动过程中频率计数器已经开始工作,为了保证频率计数的正确性,可设计cnt计数器,丢弃初次计数值。最后,将有效的计数值输出给fre_data。

3 仿真验证

使用ModelSim对可编程逻辑进行仿真。测量对象为1000 Hz方波信号,时钟频率为33 M,因此时钟计数值应该是33 000。任选信号周期内的一个时刻作为系统复位点,仿真结果如图3所示。从图3可以看出,fre_data的值在第三个start信号凸起后变为33 000,与理论值完全一致,说明设计有效。

4 实测数据

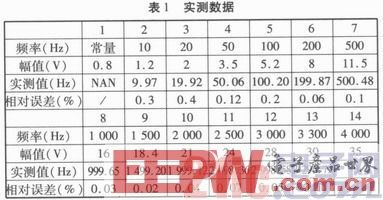

使用信号发生器提供不同频率的正弦信号,对系统进行实测,所选取的频率测试点覆盖整个实际应用的频率范围,即20~3 300 Hz,且可以验证可编程逻辑电路的数字滤波及延时判断功能。同时,为了更好的模拟发动机实际情况,正弦信号的幅值应随着其频率的增大而增大。实测数据如表1所示。

从表1可以看出,当输入信号的频率小于1Hz时,系统的延时判断功能生效,实测值为NAN(无穷大);当输入信号的频率大于3 300 Hz时,系统的数字滤波功能生效,实测值为0;当输入信号的频率介于1~3 300 Hz之间时,实测值的相对误差不超过0.4%,与实际频率基本一致。

5 结束语

文章提出了一种基于FPGA的多通道频率测量系统的实现方法,主要创新点是利用可编程逻辑芯片搭建数字滤波电路,通过逻辑分析判别输入信号是否切断并做出响应,符合实际应用的需求。系统的扩展性强,电路结构相对简单,仿真及实测结果表明滤波效果明显,测量精度较高,在工程领域具备适用价值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码