一种基于SMS4的加密通信可编程片上系统设计

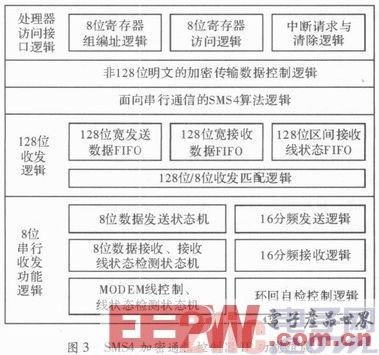

8位串行收发功能逻辑提供8位数据收发、接收线状态检测、MODEM线控制与线状态检测功能。128位收发逻辑使128位SMS4密文和8位串行收发数据之间的传输能够平滑、顺畅地进行。面向串行通信的SMS4算法逻辑在完成128位SMS4加解密运算的同时,还具备FPGA资源利用少、加解密吞吐量与串行通信吞吐量匹配的特点。非128位明文的加密传输数据控制逻辑重点解决非128位明文的加解密运算和串行传输问题。处理器访问接口逻辑为处理器提供8位数据位宽的访问接口,使处理器对SMS4加密通信控制器IP的访问方式尽可能地接近于一般的8位串行通信控制器。

2.2 加密通信IP核仿真验证

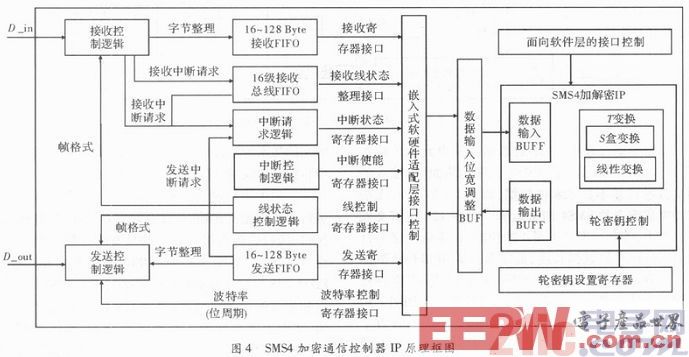

本文设计了SMS4加密通信控制器IP核完成加密通信,图4为SMS4加密通信控制器IP的原理框图。

采用Altera公司的Quartus II FPGA开发工具完成SMS4加密通信控制器IP的HDL代码编译。

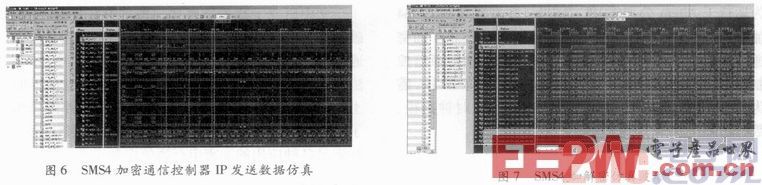

使用ISim仿真器进行SMS4加密通信控制器数据接收与发送仿真,得到仿真波形,如图5和图6所示。SMS4加密通信控制器IP对加密算法、数据收发、数据缓冲、接收线状态等功能进行了模块化设计,各个模块既相对独立又有机组合,可完成各自功能,不同模块之间进行数据和信号的交换实现时序控制、信息交互,从仿真结果可看出,SMS4加密通信控制器IP在不影响通信吞吐量的情况下,实现了数据的SMS4的加解密处理。

如图5所示,SMS4加密通信控制器IP接收数据通过信号wb_cyc_i作为计数器,每接收一个有效数据,产生一次脉冲。we_sel_i表示接收控制器片选信号,在接收期间保持为高;wb_adr_i表示数据地址,wb_dat_i则表示接收数据值。

如图6所示,SMS4加密通信控制器IP接收数据通过信号wb_cyc_i作为计数器,每接收一个有效数据,产生一次脉冲;we_sel_is表示发送控制器片选信号,在发送数据期间保持为低。wb_adr_i表示数据地址,wb_dat_i表示接收数据值。

面向串行通信的SMS4算法逻辑设计,并已集成到SMS4加密通信控制器IP中。使用ISim仿真器对SMS4算法逻辑的Verilog代码进行波形仿真,输入128bit数据,进行加解密,其仿真波形如图7所示。

从图中可看出,SMS4加密IP利用points计算通信量,图7的通信量为1 024bit,data_in表示输入加密数据,addr_wr表示加密过程中的地址转换;data表示输出解密后的密文。

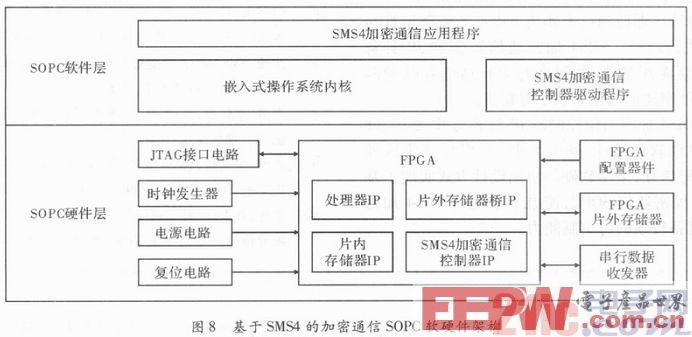

2.3 基于SMS4的加密通信SOPC软硬件架构

基于SMS4的加密通信SOPC软硬件架构如图8所示,分为SOPC硬件层和SOPC软件层。SOPC硬件层由电源、复位、时钟、JTAG接口、FPGA、配置器件、存储器、串行数据收发器等电路组成,其中FPGA是核心器件,内部集成了处理器IP、存储器及桥IP、SMS4加密通信控制器IP等。 SOPC软件层主要南嵌入式操作系统内核、SMS4加密通信控制器驱动程序、SMS4加密通信应用程序等部分组成。

SOPC硬件功能方面,电源电路、复位电路、时钟发生器为SOPC提供必须的电源供应、上电和硬件复位信号、时钟同步信号。JTAG接口电路用于调试SOPC的硬件逻辑和软件程序,同时也用于在线下载FPGA配置文件。FPGA配置器件存储FPGA静态配置,在上电时自动对FPGA进行配置;由于FPGA内部存储资源有限,需外扩RAM、Flash等片外存储器。串行数据收发器实现TTL电气接口信号与RS-232/422电气接口信号的转换,使串行数据收发信号能适应远距离传输环境。

SOPC软件功能方面,嵌入式操作系统内核提供基本的存储管理、设备管理、中断管理及任务调度等功能。SMS4加密通信控制器驱动程序将SMS4加密通信控制器抽象成一个以文件方式访问的设备,供应用程序调用。SMS4加密通信应用程序实现明文数据的收发,由于SMS4加密通信控制器IP可屏蔽密文传输过程,应用程序中无需进行加解密处理。

基于SMS4的加密通信SOPC硬件集成,需软件集成及性能分析。SMS4加密通信SOPC主要依靠专用串行接口扩展模块的FPGA芯片进行硬件集成,图9为运行于Altera公司SOPC Builder开发环境的SMS4加密通信SOPC硬件集成界面。如图所示,SMS4加密通信SOPC集成有NiosII处理器IP、SMS4加密通信控制器IP、SRAM和Flash的存储器控制IP等IP核,需为各IP核指定Avalon总线互连拓扑关系、时钟路径、数据访问空间及中断路由等。

3 结束语

面向串行通信优化SMS4算法的硬件实现,通过基于8位异步模式的128位数据串行收发技术实现SMS4加解密和串行通信的深度整合,通过非128位明文的加密传输数据控制技术实现SMS4加解密运算与处理器无关,设计的SMS4加密通信控制器IP具备FPGA逻辑资源用量小、加解密与串行通信吞吐量匹配、处理器加密通信处理负载小等特点。

通过SMS4加密通信控制器IP封装与IP复用、硬件抽象层驱动软件设计、基于SOPC开发环境集成处理器IP及配套IP,采用软硬件协同设计方式实现了基于SMS4的加密通信SOPC,使电子系统的SMS4加密通信功能具备较强的可定制能力。

文中研究了基于硬件实现加密串行通信功能,防破解能力强、处理器负载轻,进而提高了应用系统串行通信的安全性,有较好的推广应用价值。其中,核心算法采用SMS4算法,有力支撑了密码学研究成果的本土化,为满足国内信息安全技术的自主可控需求作出了一定贡献。另外,文中设计的可定制SOPC,也可较好满足各种应用的加密串行通信定制需求。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码