软件定义无线电应用的转换器增益和时序误差实时校准

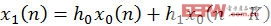

如果x0和x1表示两个子ADC的输出,而校准信号是其输入,可以使用公式1来表示它们,下面的表达式将这两路信号连接起来(忽略了噪声):

(公式2)

这一线性滤波公式的系数h0和h1可以明确地对应于增益g和时序Δt误差:

(公式3)

可以使用一阶近似,而设计中的失配误差比较小,将这一非线性方程组线性化并求逆

估算算法包括以下三个步骤:

1. 提取出校准信号,使用LMS算法,从子ADC的输出消除它,产生离散时间信号x0和x1。这一算法要求在校准频率上应用数字余弦/正弦参考信号。使用容量 为4K (实际中,K64)的小规模查找表(LUT)来产生余弦信号。通过简单的将余弦信号延时K来产生正弦信号。

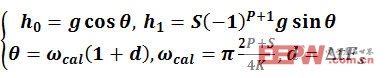

2. 如图2所示,使用LMS算法,从提取出的x0和x1信号中自适应估算出系数h0和h1。

3. 从公式3中得到的线性方程组中计算出增益和时序误差。

图2:通过2抽头数字自适应滤波器进行增益和时序误差背景估算。

得到估算结果后,增益和时序误差被输入到数字校准引擎中。使用简单数字乘法器补偿增益。采用修正的小数延时滤波器对时序误差进行校准。通过多相和对 称方法来降低滤波器实现的复杂度。估算和校准引擎都都以子ADC的采样速率运行,为进一步优化,估算模块还可以采用降采样的方案。

方法验证

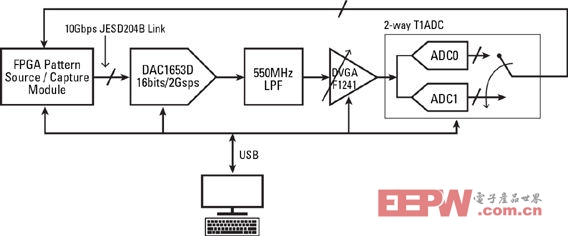

一路合成测试信号包括:中心是300 MHz的一路TM3.1、20 MHz LTE载波,以及一路253.44 MHz、-35 dBFS校准正弦波。对应于S=1、K=8、P=2K,可以使用图3中的测试设置来产生这些信号。这一设置具有低噪声和高线性度D/A转换器以及 DVGA,因此,其动态范围非常高。我们采用了集成了高分辨率可调增益和时序误差功能的商用14位 / 500Msps TIADC。通过FPGA采集ADC原始数据,使用Matlab软件,由IDT校准算法处理这些数据。TI ADC的增益和时序误差分别被设置为大约0.5 dB和5 ps,以仿真最差情况。

图3:测试设置结构图。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码