基于FPGA多路机载冗余图像处理系统的设计方案

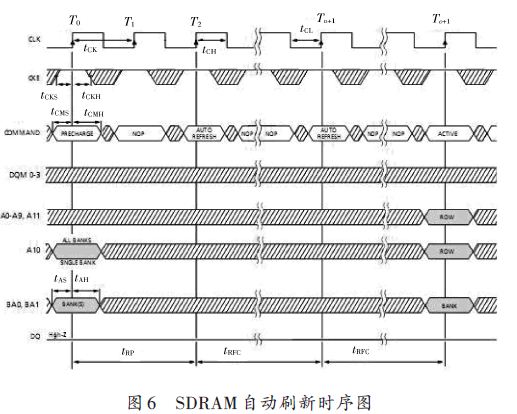

SDRAM在完成读写操作的同时还需要完成每64 ms全行(4 096行)自动刷新操作,为所有行进行充电,不然就会导致SDRAM内的数据丢失。自动刷新时序图如图6所示。

这里将自动刷新操作穿插在读写当中,经计算为15 μs 需进行一次自动刷新操作,通过一个计数器每15 μs 发起一次自动刷新请求,程序检测到自动刷新操作请求后进行自动刷新操作然后再进行读写操作,自动刷新操作占用10个时钟周期。图7为写和读之间穿插了一次自动刷新操作,操作命令为10001.

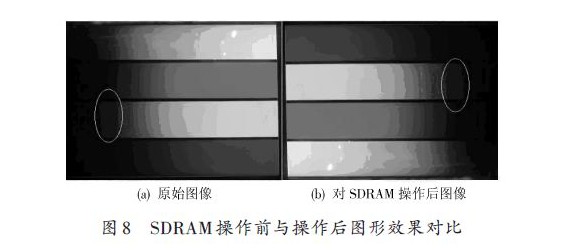

测试结果证明,该缓存系统实现了预定功能,可以对视频数据进行更方便的操作与管理。SDRAM操作前与操作后图形效果对比如图8所示。

4 结语

本文介绍了某机载实时冗余视频图形处理系统的设计方案,该系统利用FPGA设计结构化状态机实现对 SDRAM的控制,完成了对数据的缓存设计,实现了对多路DVI视频冗余信号的解码、编码、实时处理以及输出显示。该系统电路设计简洁,具有速度快、可靠性高、灵活性强和功能可扩展等优点。并且,由于信号通道增加冗余设计,因而加强了系统显示的稳定性和可靠性。本系统已经投入使用,其性能可靠、稳定,实用性强。该方法值得推广。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码