高性能信号处理通用平台研究

2硬件设计

该信号处理模块符合VME标准,采用6U双高板结构,模块内部硬件实现上可划分为四级总线结构,分别是局部总线、全局总线、PCI总线以及VME总线。在局部总线上的资源有:SBRAM、SDRAM及双向FIFO;全局总线上的资源有:PCI总线接口、SRAM、FLASH;PCI总线上的资源有:RaceWay接口、HOST PCI的桥、PCI VME的桥以及PCI DSP的桥;VME总线上的资源有:

VME总线接口。

2.1存储系统设计

信号处理模块的存储器空间包括:局部总线空间和全局总线空间。局部总线空间由局部控制寄存器空间、SBSRAM空间、SDRAM空间、FIFO空间、内部程序存储器空间、内部数据存储器空间和内部外设空间构成。全局总线空间由全局FLASH空间、全局SRAM空间、全局总线控制寄存器空间和PCI接口空间构成。

EMIF是外部存储器和TMS320C6701片内各功能单元的接口,DSP访问片外存储器时必须通过EMIF.

EMIF具有很强的接口能力,其数据总线宽度为32b,可寻址空间为4GB,可以与目前几乎所有类型的存储器直接接口,数据吞吐能力最高可达667MB/s.EMIF支持的器件类型包括:同步突发静态RAM(SBSRAM)、同步动态RAM(SDRAM)、异步器件(包括异步SRAM、ROM和FLASH等),异步接口速度、时序可编程,可以配合不同的器件。

EMIF处理的外总线请求有四种来源:片内程序存储器控制器发出的取指请求,片内数据存储器控制器发出的数据存取请求,片内DMA控制器的请求,外部共享存储器设备的控制器发出的请求。当同时有多个部分申请外总线时,由EMIF根据设置的优先级进行仲裁,然后响应各个申请。一旦某个申请者根据优先级获得了处理权,这一处理权会一直保留到该申请者放弃请求或者是有更高优先级的申请者提出申请,其间即便有新的申请出现,EMIF也不会受理。在新的申请开始得到处理之前,对于已经获得处理权的前一个申请者,其尚未完成的操作部分可以优先继续完成。

2.2全局总线设计

模块内全局总线可由4个DSP、PCI接口芯片中的任何一个来占用,全局总线仲裁电路的设计是该模块设计中的一个要点。考虑到PCI接口是整个系统信息交换最重要的通道,它的利用率的高低直接决定了系统的性能,所以将其优先权定为高,将DSP的优先权定为低。DSP之间的仲裁采用轮转优先级仲裁算法。

DSP通过异步接口空间访问全局总线,由于TMS320C6701的异步接口空间仅能够提供4MB的地址空间,为了克服芯片的这个限制,采用页面的机制扩充异步接口空间,使该空间最大可访问的空间达到2GB.把DSP的EMIF提供4MB的异步接口空间分为两部分,低2MB(即A21=0)用于访问全局资源,高2MB用于访问每个DSP的局部资源。采用这种DSP异步接口空间的划分方法简化并加快了译码。当复位时每个DSP的页面寄存器都被置为0×0000 0000,它会自动通过异步接口空间指向FLASH,实现自举。当一个DSP获得全局总线的访问权后,由该DSP的页面寄存器决定全局总线地址的高11位(GA31:GA21),全局总线地址的低位(GA20:GA2)直接由该DSP驱动,GA1和GA0由译码得到。

通过以下计算公式可以计算页面值和页内偏移量:

页面值=(全局总线上的地址)

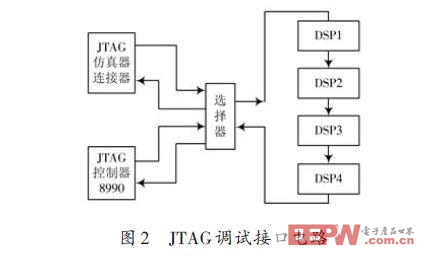

2.3调试接口

JTAG是基于IEEE 1149.1标准的一种边界扫描测试方式。TI公司为C6000系列DSP提供了JTAG端口支持,结合配套的仿真软件可以访问DSP的所有资源,包括片内寄存器以及所有的存储器,从而提供了一个实时的硬件仿真与调试环境,便于开发人员进行系统软件调试。

该信号处理模块提供两种方式的JTAG调试。一种方式是使用TI的XDS510仿真器和JTAG仿真协议给信号处理模块下载程序,在软件开发和调试时控制程序的执行。另一种方式是使用TI的代码编译开发环境和Pentek的SwiftNet通信协议给信号处理模块下载程序和进行调试。这两种方式可通过一个选择器进行选择使用。

该信号处理板上有4片DSP,需要进行多处理器仿真调试,将DSP的JTAG端口和JTAG仿真器或JTAG控制器间以菊花链方式互连。JTAG调试接口电路如图2所示。

关键词: 信号处理 TMS320C6701 通信网络 EMIF

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码