IXP425和DM642的会议电视多点控制单元硬件设计

2.2 网口设计

IXP425内部有3个与XScale核并行工作的网络处理机NPE,能对外部提供2个MII接口,并行工作的原理使得网络处理性能较好,支持802.3协议内容,标准的MII接口只需外接PHY物理接口芯片,平台中采用了Intel的LXT972A,即能完成与外界数据的交互。当然,变压器的使用也是必须的,利用了HALO生产的TG110-S050N2与RJ45接口挂接,连接示意图如图4所示。由于IXP425内置了MAC控制器,完善的MII接口使得平台的网络应用比较简单而具有针对性。

2.3 音/视频处理模块设计

2.3.1 PCI接口设计

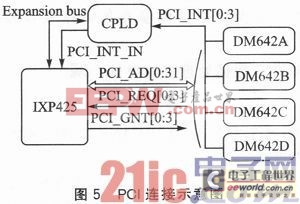

IXP425 PCI控制器外部挂了4片DM642,总线为33MHz,连接示意图如图5所示。IXP425 PCI总线主要完成对DM642的启动加载、芯片配置管理、PCI总线仲裁和媒体流调度。DM642芯片组主要完成音/视频媒体流的编码、音/视频合成的功能。目前的容量为4路音/视频合成,视频算法为H.264,语音算法为AAC、G.723.1等。

其中,DM642A占用IXP425的PCI时隙1,DM642B占用IXP425的PCI时隙2,DM642C占用IXP425的PCI时隙3,DM642D占用IXP425的PCI时隙4,其有差异的对应引脚互连如下:DM642A与IXP425的PCI引脚对应。PCI中断控制信号由CPLD进行会聚后上报给CPU,CPU通过读取CPLD内部的中断寄存器来判断外围PCI设备的中断事件。

2.3.2 音/视频处理模块最小系统设计

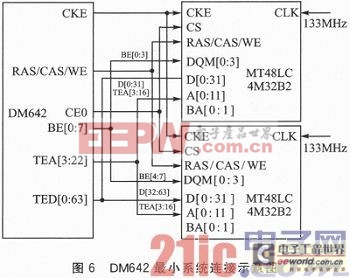

EMIFA允许无缝连接多种SDRAM,由于选用的SDRAM大小为64 MB,根据DM642 EMIFA的接口准则,DM642最小系统如图6所示。

芯片选择由CE0完成,选用2片16MB大小的SDRAM进行位扩展后,最大寻址空间为32MB,行地址选通为A[3:10],列地址选通为A[3:14],块选择(bankselect)为A[15:16],故使用DM642地址线A[3:16]。DM642内核工作在50M×12 Hz的模式下,EMIF接口工作在25M x 5.33 Hz,PCI接口工作在33 MHz时钟频率下。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码