基于FPGA的基带64×64数据分配矩阵设计方案

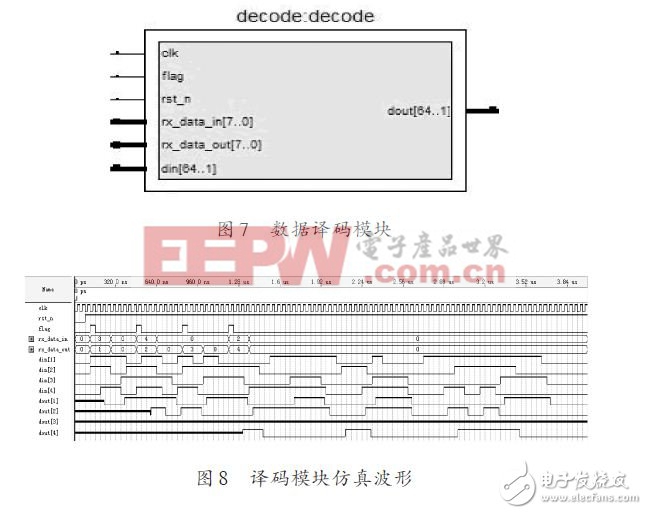

EXT-INDENT: 0px; MARGIN: 0px 0px 20px; PADDING-LEFT: 0px; PADDING-RIGHT: 0px; FONT: 14px/25px 宋体, arial; WHITE-SPACE: normal; ORPHANS: 2; LETTER-SPACING: normal; COLOR: rgb(0,0,0); WORD-SPACING: 0px; PADDING-TOP: 0px; -webkit-text-size-adjust: auto; -webkit-text-stroke-width: 0px"> 由于64×64的仿真很繁琐且不易操作,所以对4×4的译码模块进行仿真,仿真结果如图8所示,输出1与输入3相连,输出2与输入4相连,输出3悬空,输出4与输入2相连。

4 结语

本文采用FPGA作为实现控制逻辑的核心部件,提出了基于FPGA的基带64×64 数据分配矩阵设计方案,并介绍了上位机的软件设计思路和FPGA的内部编程实现及仿真。经验证本系统基本能实现基带数字信号的分配路由,从而证实了该方案具有规模大、成本低、高速等特点,可广泛应用于大规模基带数字系统测试及信号程控分配调度中。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码