数字基带芯片揭秘:高灵敏度接收机跟踪环路设计

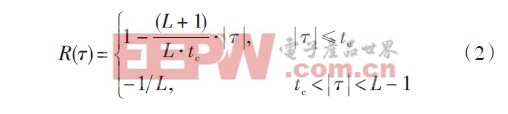

分别表示鉴相器的增益系数和鉴相特性函数。GPS C/A码的码长为L = 1 023,BD C/A码的码长为L = 2 046,码元宽度为tc =20 ms,其相关函数为:

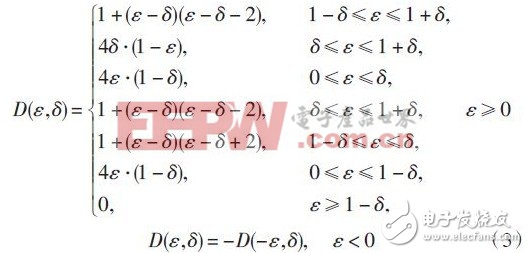

由此可得鉴相器的鉴相特性函数:

鉴相特性函数为相关间隔与码相位偏差的函数。

若定义(-δ,δ) 为鉴相线性范围,鉴相特性函数在ε = 0 处的斜率D′(ε,δ) 为DDLL环的鉴相增益,Dmax (ε,δ) 为跟踪牵引范围。

1.3 载波跟踪环路设计

载波的同步包括了捕获和跟踪两个过程,载波捕获即多普勒频移的粗略估计已由快捕通道的捕获算法完成,而精确的载波相位及多普勒频移跟踪则通过反馈跟踪控制环路实现。本方案采用一种非相干的FLL环--叉积自动频率跟踪环(CPAFC)加锁相跟踪算法作为载波跟踪方法。在通过捕获算法进行伪码捕获后,载波多普勒频移范围被“牵引”到了500 Hz,为了使多普勒频移进入叉积鉴频器的线性工作范围,算法上首先采用叉积鉴频器将频率从几百赫兹降到几赫兹,然后利用锁相环进行精确的频率跟踪。

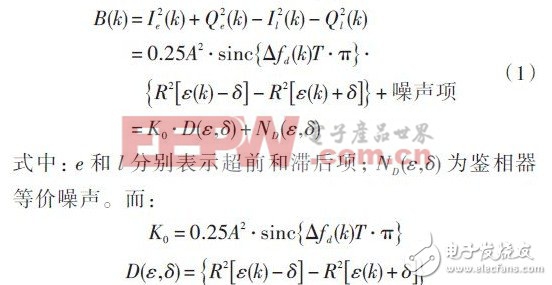

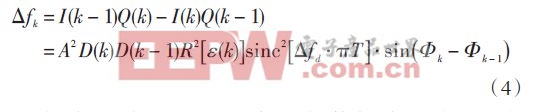

叉积自动频率跟踪环鉴频算法为:

假定连续量测过程中调制数据位不变,即有D(k)D(k - 1) = 1.在预检积分时间内载体机动造成的频率偏移可视为恒值,则有Δfd ≡ Δfd (k) = Δfd (k - 1) 成立。而由于Φk = Δfd (k) - tk + Φ0 ,则:

输出与单位时间间隔内的相位变化成正比,可以用此输出量控制载波DCO 以达到频率跟踪的目的。该算法上要求在同一数据位内计算,在信噪比较低的情况下仍能取得较好的性能[7]。

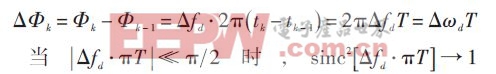

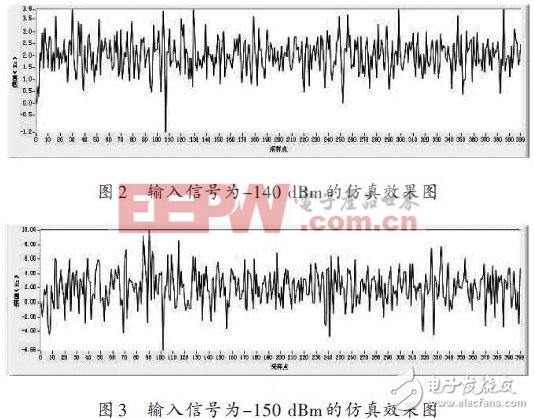

设定相干积分时间为20 ms,载波固定频偏为2 Hz,环路带宽为10 Hz,当输入信号由-140 dBm 减弱至-160 dBm 时的仿真效果图如图2~图5所示。

由图2~图5 可知,当输入信号功率小于-150 dBm时,采用传统的环路跟踪策略已经不能实现稳定的跟踪,必须要设计新的跟踪方法。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码