在ZVS拓扑中选择最优的死区时间

很显然,ZVS导通只有在可用的死区时间Tdt内才可能实现。

输出MOSFET的栅极电容放电,电压降到Vth以下,

输入MOSFET的输出电容器完全放电,电压接近零伏。

图3显示的是在分析过程中使用的简化的栅极关断电路。由于所有电容都是Vds的函数,可以在计算过程中使用等效的充电标准。栅极电荷放电分为3个明显的阶段,如图4所示。

T0-T1:栅极电源电压从Vgss到平坦的Vgp阶段,Ciss放电,假设关断电流是恒定的。在这段间隔时间里,Igoff电流受到驱动能力的限制,而不是栅极电阻的限制。

T1-T2:常规的平台时间是从Vds上升到Vin的这段时间,由于振铃效应,Vds会超过Vin。栅极电流受到栅极环路总电阻的限制。

T2 – T3:在输出MOSFET里的电流下降时间。

可以用这些公式计算三个时间间隔:

用来计算TGSP的Ciss0不是从数据表里找来的,只是当MOSFET完全导通,Vds = 0V情况下的数值。对于具有极高元胞密度、沟槽式栅极和电荷均衡结构的超低RDS(ON) MOSFET,Ciss0可能比在中压条件下的Ciss高4到5倍。这里没有功率损耗,但这段间隔时间会占到可用死区时间的主要部分。TGPT的计算公式定义了根据驱动状况实现关断过程中的总电压上升时间和电流下降时间。这是不充分的粗略估算,因为电流下降时间取决于很多外部参数,例如PCB印制线的电感、封装的源电感及输出电压。这些因素决定了在栅极驱动上的初级环路电流的di/dt。然而,这里要关注的焦点问题是输入MOSFET在达到零电压状态,可以用过另一种方式来确定这种状态。既然高边MOSFET里的电降到零,流在低边MOSFET里的电流分量也为零。这样就可以简单地估算输出电容放电所需的时间,大约是Lpcb 和 Coss的一个谐振周期的四分之一。

假设PCB印制线的电感远小于泄漏电感Llk,在TDSD时间内,变压器的回路电流不变。有了这个假设后,我们就可以描述死区时间Tdt的完整时序要求。

对于具有高Vth的器件来说,最终的计算结果有点保守。在栅极电压达到Vth前的上升时间要更长一些,这段时间会加到死区时间里。

在IBC转换器上的测试结果

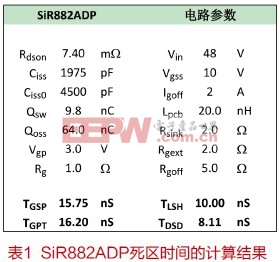

上面的分析已经在SiR882ADP得到验证,这款高性能MOSFET定位在高频DC-DC转换器。器件的相关规格见表1。测试平台是在200kHz下工作的48V~9.6V IBC转换器。最初的设计把死区时间设定为20ns。根据表1的数值,显然这个死区时间是足够的。

图5a至图5c显示的是50ns、75ns和20ns这三个不同死区时间的开关节点的波形。图6显示的是整个转换器的功率损耗,功率损耗是不同死区时间的函数。最小损耗的最优开关发生在死区时间为50ns的情况下,跟计算结果一样。在20ns死区时间时,低边MOSFET导通,开关节点电压为Vin,会产生共通损耗。75ns情况下的波形看起来很清楚,具有额外的安全裕量,二极管导通的时间也增加了。图6显示了这个影响:随着电流加大,二极管损耗逐步增加。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码