ARM指令寻址方式之: 数据处理指令的寻址方式

4.1 数据处理指令的寻址方式

4.1.1 数据处理指令的寻址方式概要

数据处理指令的基本语法格式如下。

opcode> {cond>} {S} Rd>,Rn>,shifter_operand>

其中shifter_operand>有下面11种形式,如表4.1所示。

表4.1 shifter_operand>的寻址方式

语 法 | 寻 址 方 式 | |

1 | #immediate> | 立即数寻址 |

2 | Rm> | 寄存器寻址 |

3 | Rm>, LSL #shift_imm> | 立即数逻辑左移 |

4 | Rm>, LSL Rs> | 寄存器逻辑左移 |

5 | Rm>, LSR #shift_imm> | 立即数逻辑右移 |

6 | Rm>, LSR Rs> | 寄存器逻辑右移 |

7 | Rm>, ASR #shift_imm> | 立即数算术右移 |

8 | Rm>, ASR Rs> | 寄存器算术右移 |

9 | Rm>, ROR #shift_imm> | 立即数循环右移 |

10 | Rm>, ROR Rs> | 寄存器循环右移 |

11 | Rm>, RRX | 寄存器扩展循环右移 |

数据处理指令的寻址方式根据shifter_operand>的不同,相应的分为11种。

4.1.2 指令解码

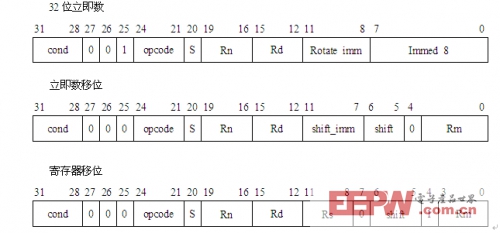

图4.1显示了数据处理指令不同寻址方式下的解码格式。

图4.1 数据操作指令编码格式

编码格式中各域含义如下。

· opcode>:确定具体指令。

· S:标识指令是否影响程序状态寄存器CPSR条件标志。

· Rd:指令操作的目的寄存器。

· Rn:指令第一源操作数。

· bit[11∶0]:移位操作,详见本章移位操作一节。

· bit[25]:被用来区分是立即数移位操作还是寄存器移位操作。

如果指令编码出现下面情况:bit[25] = 0并且bit[4] = 1并且bit[7] = 1,则指令并非数据处理指令,它可能是Load/Store指令或算术指令。

4.1.3 移位操作

数据处理指令是在算术逻辑单元ALU中完成。ARM处理器一个显著特征就是可以在操作数进入ALU之前,对操作数进行指定位数的左移或右移操作。这种功能明显增强了数据处理操作的灵活性。

移位操作可能产生进位,更新程序状态寄存器CPSR的进位标志C。移位操作有下面3种基本方式。

1.立即数方式

没有任何一条ARM指令可以包含一个32位的立即数,数据处理指令编码格式中,第二个操作数有12位。指令的编码格式如图4.1所示。

指令中的立即数是由一个8 bit的常数移动4 bit偶数位(0,2,4,…,26,28,30)得到的。所以,每一条指令都包含一个8 bit的常数X和移位值Y,得到的立即数=X循环右移(2×Y)。

注意 | 8位立即数一定要移偶数位。 |

下面列举了一些有效的立即数。

0xFF、0x104、0xFF0、0x FF00、0x FF000、0x FF000000、0x F000000F

下面是一些无效的立即数。

0x101、0x102、0x FF1、0x FF04、0x FF003、0x FFFFFFFF、0x F000001F

下面是一些应用立即数的指令。

MOV r0,#0 ;送0到r0

ADD r3,r3,#1 ;r3的值加1

CMP r7,#1000 ;r7的值和1000比较

BIC r9,r8,#0x FF00 ;将r8中8~15位清零,结果保存在r9中

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码