FPGA最小系统之:实例2 在Xilinx的FPGA开发板上运行第一个FPGA程序

3.综合及仿真

(1)综合。

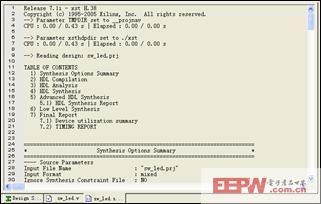

在“Process View”对话框里面双击“Synthesize – XST”,开始进行工程的综合,如图2.81所示。

综合主要检查源文件程序里面的语法错误(Check Syntax),双击“View Synthesis Report”可以观察综合的结果报告,如图2.82所示。

图2.82 综合报告

如果在这步发现源程序的设计语言有语法毛病,就会弹出Error警告。这样就可以根据报错的位置,在源程序里面查找错误位置,修改好以后重新进行综合,直至无错误为止。

(2)综合后仿真。

这里的仿真是综合后的仿真,也可以称为功能仿真。仿真时并不考虑工程的约束条件及器件的资源使用状况,因此不会产生仿真延迟。这里使用的是ISE自带的仿真工具进行综合后仿真。下面是仿真的步骤。

① 产生仿真文件。

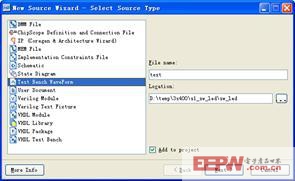

如图2.76的方式,在“New Source”对话框里面选择创建Test Bench Wavefrom文件,如图2.83所示。

单击“Next”按钮,在如图2.84所示对话框中为Test Bench指定源文件。如图所示在源文件对话框中只有一个文件,这是因为我们只为工程添加了一个设计文件。如果我们为工程添加了几个设计文件,在这个对话框中,将出现多个源文件。此时用户可以选择需要进行仿真的源文件即可。

图2.83 新建Test Bench对话框

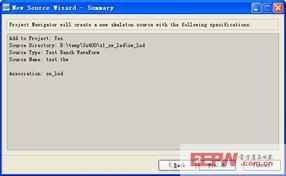

在本训练中,将要进行仿真的源文件是sw_led,如图2.84所示。单击“Next”按钮完成仿真文件的产生,如图2.85所示。

图2.84 为Test Bench指定源文件

图2.85 Test Bench信息对话框

单击“完成”按钮,ISE将创建名为test.tbw的仿真文件,同时弹出如图2.86所示的对话框。在该对话框中,用户可以对仿真的时间参数进行设置。

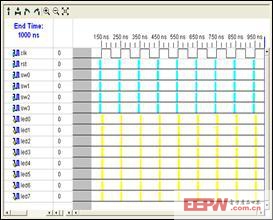

在这个对话框中,包括时钟信息、时钟时间信息、全局信号、仿真时间等多个参数都可以进行设置。按照仿真需求修改好时间参数以后,单击“OK”按钮就能在ISE的工作区里面看见新建的波形文件了,如图2.87所示。

在波形文件里面,clk是时钟信号,在前面的时间参数设计里面已经设置好了。用户若需要对时钟进行更改,可选择执行“Test Bench”→“Rescale Timing…”命令,弹出修改时间参数的对话框,如图2.88所示。

图2.86 仿真时间参数设置对话框

图2.87 时钟波形 图2.88 修改时间参数对话框

同样也可以执行“Test Bench”→“Set End of Test Bench…”,在弹出的对话框里面修改仿真波形的截止时间,如图2.89所示。

图2.89 截止时间设置对话框

单击“OK”按钮就会发现仿真波形的时间长度由1000ns变成了2000ns。

② 添加仿真激励。

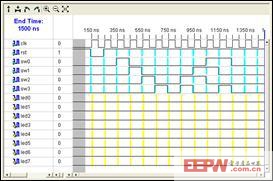

要进行仿真,还需要为仿真添加激励。这里可以通过点击波形图中的蓝色方块来设置输入波形电平的高低,如图2.90所示。

图2.90 设置输入电平

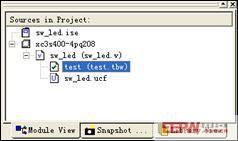

设置好以后一定不要忘记保存波形文件。保存以后就会在工程浏览器的当前工程的子目录下看见刚生成测试的文件,如图2.91所示。

图2.91 保存仿真文件到工程

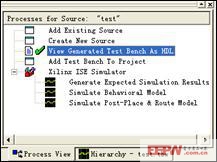

③ 仿真。

首先在工程浏览器的【Module View】里面选择“test(test.tbw)”。

图2.92 由波形文件生成测试代码

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码