LVDS的接口电路设计

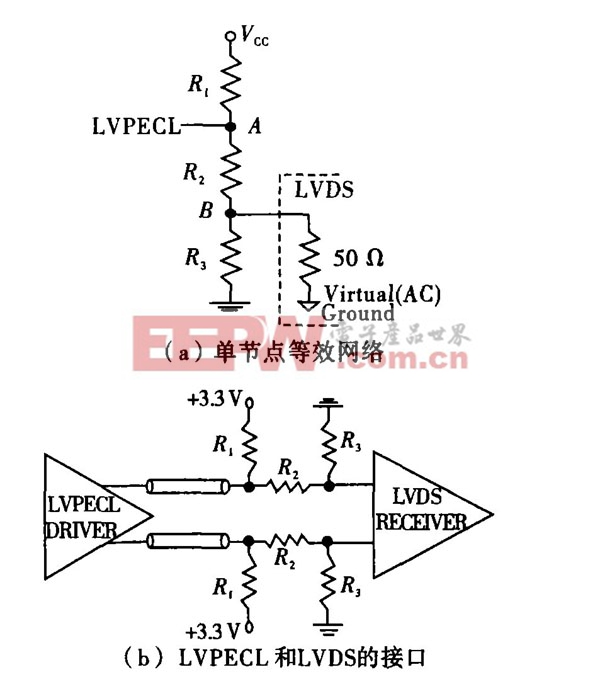

4. 2 LVPECL 到LVDS的互连

4. 2. 1 直流耦合。

LVDS和LVPECL间的直流耦合要有一个转移网络,如图2所示。首先LVPECL 输出阻抗最佳是50Ω;另外, LVPECL 电路经过衰减网络的输出信号要在LVDS的输入范围内。下面的公式可以得到电阻的值。

图2 LVPECL 和LVDS间的直流耦合

把VCC = 3. 3 V代入(1)式,得R1 = 182Ω, R2= 47. 5Ω, R3 = 47. 5 Ω,另外VA = 1. 13 V, RAC =51. 5Ω, RDC = 62. 4Ω , Gain = 0. 337.若当使用该网络连接LVPECL 的输出端和LVDS的输入端时,那么测量的共模电压VA = 2. 1 V, VB =1. 06 V.假定LVPECL 的差分输出最小是930mV,那么LVDS输入端的最小电压就是313 mV,满足了LVDS 的输入条件。另一方面, 如果LVPECL的差分输出最大是1. 9 V,那么LVDS输入端的最大电压就是640 mV,同样满足LVDS的输入规范。

4. 2. 2 交流耦合。

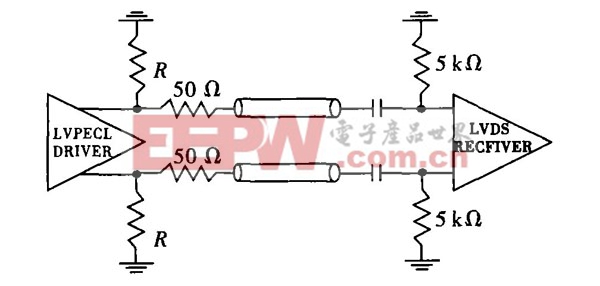

LVPECL 和LVDS间的交流耦合的电路如图3所示。

图3 LVPECL 和LVDS间的交流耦合电路

LVPECL输出通过直流偏置电阻R (142Ω~200Ω )接地。50 Ω 的串联电阻来减弱LVPECL的输出电压来满足LVDS的输入要求。在LVDS输入端每端接1个5. 0 kΩ的电阻到地用来减弱共模电压。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码