一种多通道ARINC429总线收发容错方法的研究

3 ARINC429总线接收模块设计

ARINC429总线接收模块,要实现能自动识别两种速率100 Kb/s和12.5 Kb/s,并对数据进行校验。

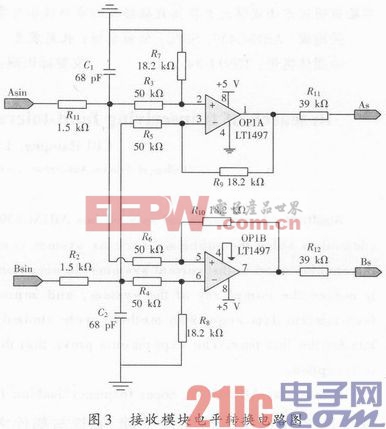

3.1 电平转换电路

和发送模块类似,接收模块在接收信号之前,也要进行电平转换,将信号转换成FPGA能识别的电平,ARINC429接收模块电平转换电路图如图3所示。

3.2 接收状态转换

接收模块主要有5个输入端口和2个输出端口,输入端口分别为:时钟clk_800khz、复位rst_n、校验方式set_od、ARINC429总线busa和busb,输出端口包括:输出数据outdata、输出使能done_rec。

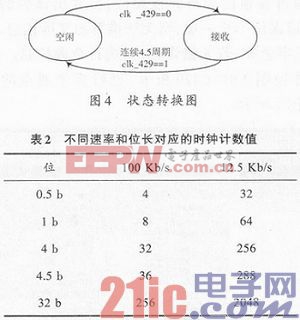

接收模块主要包括两个状态:空闲和接收。在空闲状态时,ARINC429总线上没有数据传输时,两根线busa和busb都为逻辑“0”,即clk_429=0时,说明有数据到来,转到发送状态。

在接收状态时,接收数据并移入移位寄存器,当有连续4个周期busa和busb都为0,即clk_429=1时,表示接收完成,转到空闲状态。然而,在传送最后一位数据时还有半个位周期clk_429=0,所以实际上是连续4.5个位周期如图4所示。由于ARINC429总线有两种发送速率即12.5 Kb/s和100 Kb/s,所以不同速率时的4个周期的时间也不一样,而且传输数据时每一位都有半个位周期是时钟周期,因此需列出不同速率和周期对应的时长。本设计的时钟选取为800 kHz,表2为此时钟下的计数值。

从表2中可以看出,在100 Kb/s速率下4个位周期的计数值为32,而12.5 Kb/s时为256,所以无论任何速率当计数值为32时可认为是当前传输结束。但是,12.5 Kb/s速率时的半个位周期的计数值也为32,会出现错误。所以,选择33为传输结束的计数值。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码