基于FPGA的数字量变换器测试系统设计

2.4 勤务信号发送模块实现

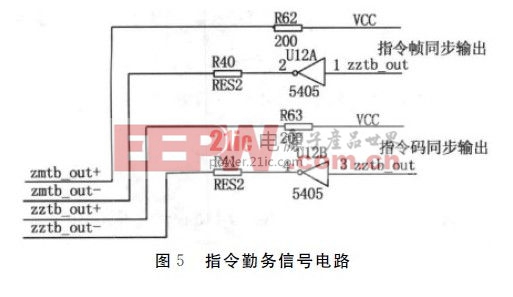

计算机字信号和指令信号都有相应的勤务信号来满足时序要求,一般勤务信号就是指帧、码同步信号,对其他信号的产生和接收起到时序基准同步的作用。指令勤务信号的电路原理如图5所示。计算机字勤务信号与其原理相同。根据系统的信号输出要求,即帧、码同步信号的幅值和电流驱动能力的要求,采用非门芯片SN5405J作为驱动电路来满足设计要求。

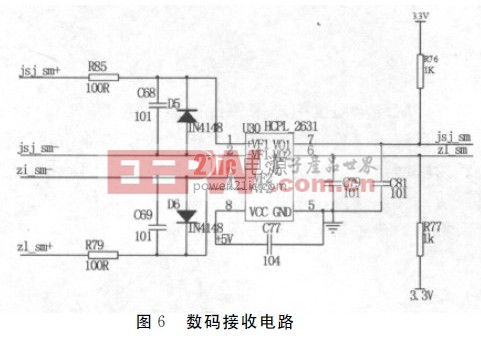

2.5 数码接收模块实现测试系统需要接收经变换器处理之后的信号,变换器以数码方式回传给测试系统,包括计算机数码和指令数码,两者的接收原理相同。设计采用光耦隔离的方式对数码信号进行接收,其电路原理图如图6所示。

光电耦合器采用TI公司的HCPL-2631,它具有电绝缘能力和抗干扰能力,并且能有效的抑制各种噪声和尖峰脉冲干扰。它的两个输入端分别接收计算机字数码和指令数码,其中在光耦输入端连接的二极管作用是用来防止信号反跳造成内部二极管烧坏。

2.6 指令信号发送模块实现

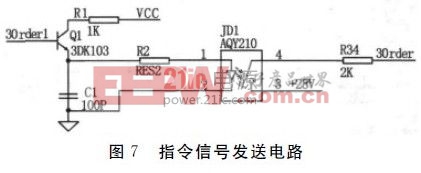

指令信号是指一种断开或闭合的开关量信号。此模块的128路指令信号全部采用光耦继电器来实现,依据参数要求选择AQY210作为控制开关的器件,它的特点是耐高压,反应速度快,使用时间长。其单路指令信号发送电路原理如图7所示。

由于指令信号的路数比较多,如果FPGA 的I/O口输出直接驱动AQY210,势必会增加FPGA的功耗。因此采用三极管对FPGA的输出信号进行电流放大来提高控制信号的驱动能力。本设计采用NPN 型三极管3DK103,图中3order1是FPGA的输出信号,其为‘0’时,三极管截止;其为‘1’时,三极管处于电流放大,流经光继电器发光管的电流13mA足以使AQY210导通。

3 系统FPGA的逻辑实现

系统主控FPGA采用的晶振是10M 和32.768M,10M的晶振经过FPGA内部分频后来产生系统全局时钟信号及帧同步信号,32.768M 的晶振来产生码同步信号;从控FPGA也通过10M 晶振来提供系统时钟。系统在上电稳定后,FPGA就会产生并发送帧同步信号(周期为25ms,脉宽为25μs),在25μs脉冲信号之后发送帧同步信号,信号的产生都是通过内部的计数器来实现的;且计算机字码同步信号8个脉冲信号为一组、共4组,指令码同步信号共16组。在时序上,计算机字信号的第1组码同步信号和指令信号的第16组码同步信号对齐。变换器在帧同步信号的上升沿的触发下,会向测试系统发送请求脉冲。当系统收到请求脉冲信号后,通过控制FPGA延时20ms,产生移位脉冲信号和计算机字信号共同发送给变换器。在时序上,移位脉冲信号的下降沿和计算机字每位的正中间对齐。通过对从控FPGA 的逻辑控制实现指令信号的发送。FPGA对上位机的命令信号解码后,将指令控制信号寄存在内部寄存器中,主控FPGA 通过串行通信的方式将寄存器中的命令发送给从控FPGA.发送时一组数据为10位,包括1个起始位、8个有效数据位和1个停止位,FPGA对串行数据解串,并重新编帧后将指令信号输出至FPGA 相应的I/O.数码的接收,都是先将数码信号编帧后存入FPGA的内部寄存器,再通过USB将数据上传至上位机。

4 系统测试结果

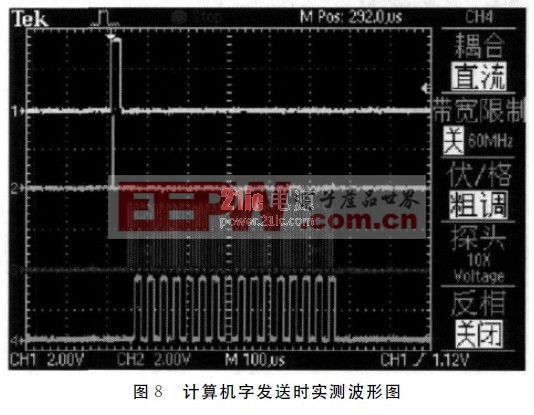

通过对系统的反复测试,来保证系统设计的可靠性。图8为上位机发送计算机字全为AAH时测到的波形,通道1是帧同步信号,通道2是数字量变换器发送来的计算机字请求信号,通道3是移位脉冲信号,通道4是系统发送的计算机字信号。

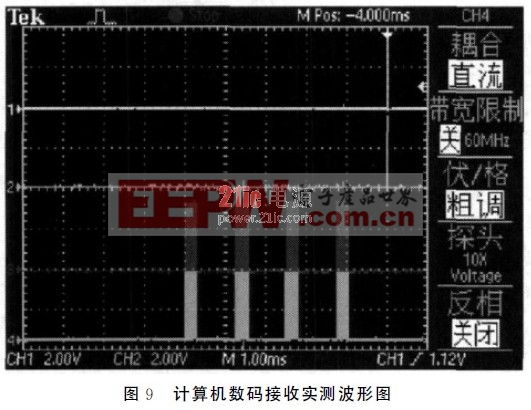

图9是系统接收计算机数码测的波形,通道1是帧同步信号,通道2是计算机字请求信号,通道3是码同步信号,通道4是计算机字数码信号。

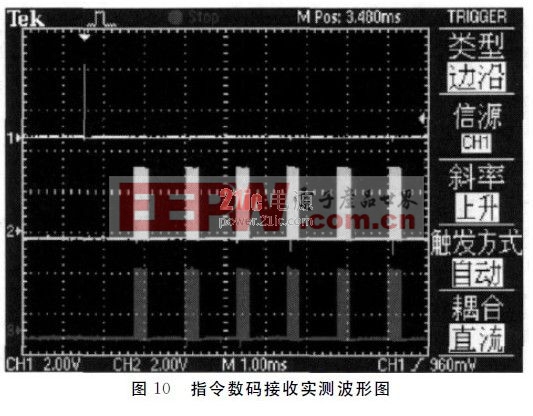

因为指令信号是以并行方式发送的,所以不涉及到时序波形的问题。图10是指令信号都发送55H 时,接收指令数码测得的波形。图中通道1是帧同步信号,通道2是码同步信号,通道3是指令数码信号。可以看出信号的效果满足设计要求而且精度较高。

5 结束语

该测试系统充分利用FPGA强大的内部逻辑功能和与外围硬件电路的设计,来达到系统的测试功能。通过测试系统和数字量变换器的联试,验证了系统各项的输出,对数字量变换器的性能做出权衡性的检测。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码