基于DDS频率源的设计与实现

3.3 编程控制

设计采用FPGA作为AD9912频率输出的控制器。AD9912正常工作DDS上电启动后,FPGA通过SDO CSB SCLK按照SPI时序向AD9912写入频率调节字(FTW)。在写完频率调节字后,将I/O_Update置位,则AD9912将映射寄存器内的频率调节字更新到寄存器,在输出口测得的频率随即改变。频率更新时间取决于SPI时序对于寄存器的写入速度,而DDS核的转换时间几乎可忽略不计。因此AD9912可作为高速跳频的频率源。

4 测试结果

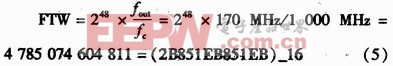

设计中采用的参考时钟频率fc=1 000 MHz要求输出频率fout=170 MHz,则其频率调节字

通过式(5)可计算得到任何的频率调节字,将其转换为16进制的数据格式后,通过FPGA严格按照SPI时序要求写入AD9912的寄存器。输出结果如图4所示,从图中可看出,AD9912的输出频率的相位噪声达到了99.56 dBc/Hz@1kHz,且输出频率准确度高杂散小,通过快速的配置寄存器就可完成快速的频率捷变,可作为跳频频率源,并能够满足设计要求。

5 结束语

根据射频短波通信系统中的频率源需求,介绍了整个频率源的实现方法,完成了使用FPGA+DDS实现射频短波频率源。采用ADI公司高端芯片AD9912,时钟输入使用AD9912内部通过锁相环(PLL)产生的低杂散高性能时钟信号,且增加外部椭圆低通滤波网络,从而有效提高了输出信号的质量。通过对输出信号的测试,证明了该方案输出在170~228 MHz的频带范围内具有相位噪声小、频率值精准及频率分辨率高等优点,可满足短波射频通信对频率源的要求。总之,该频率源设计具有外围电路简单、操作控制简便、可实现快速跳频输出以及信号频谱质量高等特点,适宜作为短波通信的频率源。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码