基于FPGA的双备份多路数据采集存储系统的设计与实

4 测试试验

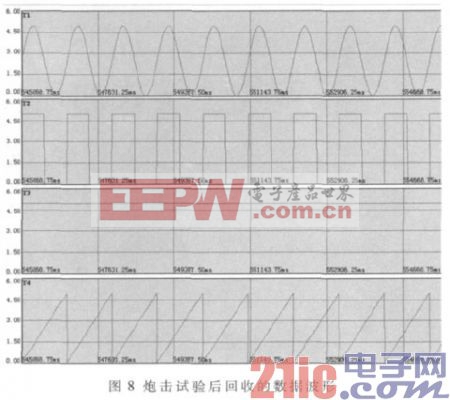

对数据采集存储系统进行炮击试验,其目的是为了考核记录器的外部结构以及内部电路板的抗过载能力。试验前,采编器采集标准的模拟弹上信源(正弦波、方波、直流量、锯齿波……依次循环),并存入存储器,然后将整个系统安装在飞行体中,飞行体以极高的速度着靶,测试采集存储系统的冲击过载能力。试验后电路板正常无损坏,而其中一块(B片)外部晶体振荡器损坏,因此,存储器采用双时钟源,正常情况下由晶体振荡器提供时钟源,在存储器回收后读取数据时,若晶体振荡器损坏,可由地面测试台提供的备用时钟作为存储器时钟源,这样就避免了回收存储器后更换晶体振荡器的麻烦。试验完成后从A片存储器中回收数据,并与试验前的数据相比较,结果一致,再从B片存储器中回收数据(由于外部晶体振荡器损坏,需用备用时钟源),与试验前的数据相比较,其波形一致,如图8所示。图8中列举了其中4个通道T1~T4的电压信号,试验表明,该系统具有很强的抗过载能力。

本文给出了基于双备份存储器的数据采集存储系统的电路设计和控制逻辑设计。在工程实践的基础上,对多通道异步时分电路的通道串扰现象提出了可行性的解决方案,同时详细地介绍了采用FPGA实现采集控制逻辑以及存储逻辑的方法,也给出了采集控制逻辑的流程和存储逻辑的设计流程。通过飞行试验,该采集存储系统采集了用来评估飞行器的各种技术指标的有用数据,实践证明,双备份设计有效的提高了数据回收的可靠性。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码