一种基于AD9854的BPSK信号产生设计

相位寄存器配置值的计算公式为(φ/2π)×214,其中φ为需要配置的相位值,对于BPSK信号,一般1号相位寄存器表示的相位值与2号相位寄存器表示的相位值相差π。频率寄存器配置值的计算公式为(f/fs)×248,其中f是需要输出的BPSK载频,即中频频率;fs为系统时钟频率,它由从REFCLK得到的外部参考时钟频率经可编程参考时钟倍频器倍频后得到。需要考虑的控制寄存器各比特定义和配置值如表2所示。

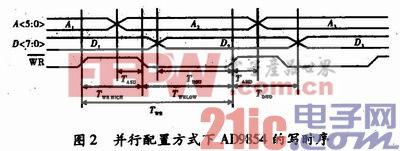

AD9854工作于并行配置方式下的写时序,如图2所示,图中最大时延TWRHGH为7ns,在编写程序时需要注意时延量。

最后的控制步骤就是编写软件,用FPGA对AD9854进行控制可以通过状态机的方式实现。

(1)采用Verilog HDL语言定义FPGA的管脚如下

modulate AD9854_Control(

input clk10MHz,

output reg[5:0]a=6'h00,

output reg[7:0]d=8'h00,

output regwrb=1’b1,

output regud=1'b0,

output regbpsk=1'b0,

output wirerefclk);

(2)给出refclk的频率为10MHz

assign refclk=clk10MHz;

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码