基于FPGA的多功能频率计的设计与实现

4 MC8051 IP Core软件设计流程

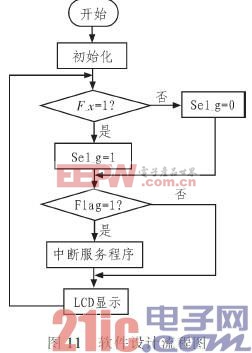

系统软件设计流程如图11所示。

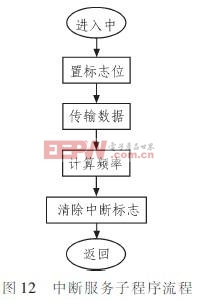

中断服务子程序如图12所示。

5 结论

文中采用Altera的cyclone II系列的EP2C8Q208C8这款FPGA芯片。设计中使用了Verilog语言对各个模块的描述设计。文中提出的数字频率计设计方案采用等精度的测量算法,以先进的FPGA可编程逻辑器件作为核心控制及运算电路单元可达到很高的测量精度要求,8051 IP Core嵌入到FPGA芯片系统,与测频模块共用同一个FPGA芯片,和传统的频率计相比大大减小了电路板的尺寸,同时增加了系统的可靠性、设计灵活性和可更改性。实现了数字系统的软件化。加入LCD液晶显示,使测量效果更加直观。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码