一种基于FPGA的三电平原理及实现方式

2.3 阻尼振荡抑制

电机开环V/F控制系统中,轻载时在某一频段内会出现电流的持续振荡,严重时甚至会引起变频器过流保护或烧毁功率模块。文献提出一种基于稳定无功电流的方法,取得了良好效果。此处采用的方法是根据电流波动的大小,在调制波中加入校正量以抑制电流波动的恶化,相比无功电流控制算法更加简单,控制原理如图2所示。

在图2中,经电流传感器测得的各相电流值inew与经滤波模块后得到的基波电流值idd求差后,得到此时电流的波动趋势,根据这种趋势的方向和大小,在原调制波上叠加usu大小的抑制量,从而形成一种负反馈,达到抑制电流脉动的作用。

![]()

式中:k为比例系数;Ts为SPWM载波周期。

2.4 中点电位平衡控制算法

中点平衡算法采用VHDL语言实现,算法参考文献,此处不再赘述。

2.5 同步分析

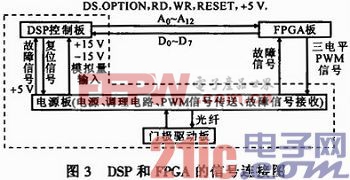

图3示出DSP与FPGA之间的信号连接图,虚线框内为原有的两电平连接图。FPGA和DSP之间通过扩展接口相连,接口信号包括双向8位数据总线D0~D7及13位地址总线A0~A12、片选信号DS.OPTION、读信号RD、写信号WR、复位信号RESET和+5 V电源。FPGA内建立的三电平PWM IP核中,译码模块通过地址总线、读写信号和片选信号产生各寄存器的选通信号,数据总线通过选通信号完成对应地址的数据寄存器的读取或写入。文献中也提到了类似的实验平台,区别在于DSP和FPGA之间无硬件同步信号,若不采取措施,则会使得DSP程序和FPGA程序的中断不同步,两者间微小的误差经过一段时间的累计会造成电流周期性脉动。此处采用软件同步的方法,通过在DSP每次中断开始时控制FPGA内三电平PWM IP核中的同步信号使能寄存器,将载波发生器清零,实现了DSP和FPGA的同步,保证了系统长时间运行的可靠性。

3 硬件条件和实验参数

在AC/DC/AC变频器上进行了开环V/F控制的实验,整流侧采用不控整流电路,输入线电压为380 V,逆变侧为二极管箝位三电平逆变器结构,负载为30 kW异步电机。开关频率设为1 kHz,采样时间为1 ms,设置的死区时间为10μs。实验主要验证了电压利用率算法和低频情况下死区补偿算法、阻尼振荡抑制算法的正确性。

4 实验结果及分析

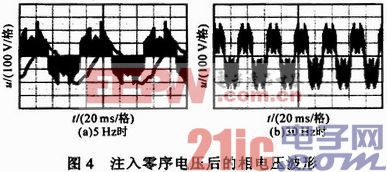

图4分别为5 Hz,30 Hz时加入零序电压注入算法的三电平相电压波形。在图4中,线性调制区内,m=1.154时,电压利用率达到100%。变频器输入、输出线电压皆为380 V。

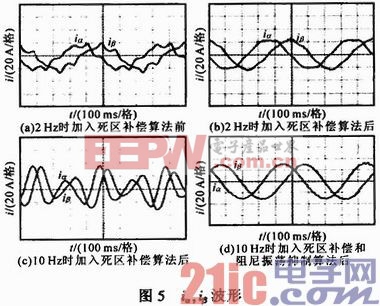

图5为流入电机的a,b,c三相电流,经3s/2s变换后得到的iα,iβ波形。图5a,b为2 Hz时加入死区补偿算法前后的波形。可见,加入死区补偿算法后iα,iβ波形明显好转。图5c为10 Hz时加入死区补偿后的波形,此时电流出现了振荡。图5d为10 Hz时加入死区补偿和阻尼振荡抑制算法的波形,可见电流振荡得到明显改善,证明了阻尼振荡抑制算法的正确性。

5 结论

采用FPGA实现了原有两电平控制板向三电平控制系统的转换,DSP负责的控制算法部分和FPGA负责的发波部分相互独立。同时,构建了三电平PWM IP核,利用硬件描述语言编写了PWM调制算法、中点电位平衡算法、死区补偿算法、阻尼振荡抑制算法及零序电压注入算法。实验结果证明了利用FPGA实现两电平向三电平转换的可行性及PWM IP核的正确性,为三电平系统的实用化提供了一种具体的实现思路。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码