基于AVR的数字滤波器滤除工频干扰的快速算法实现

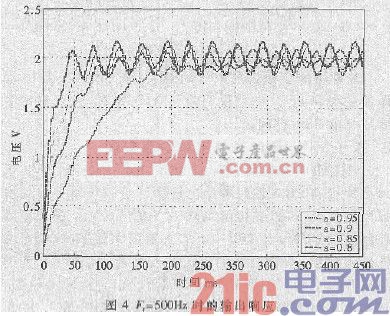

将VMLAB中虚拟示波器的显示数据导出到一个*.cvs文件中,用matlab读出这些数据,并画出不同a值对应的输出响应,如图4。从图4可以清晰看出不同a值下算法的性能变化的大致走向。

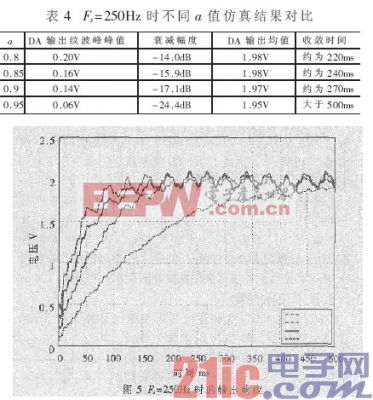

将AD的采样间隔设置为4ms,对应的采样频率Fs就变为250Hz,其它条件不变。通过VMLAB进行仿真,对比结果如表4、图5。

对比Fs=500Hz的情况,随着采样频率Fs降低,50Hz频率的幅度衰减值会逐渐增加。这主要是因为随着采样频率降低,低通滤波器的截至频率fc也随之降低,相应的滤波器在50Hz处的衰减也就越来越低。根据奈奎斯特低通采样定理,当采样频率小于100Hz时,由于信号频谱混叠,滤波器对50Hz信号的滤波效果将会变差。如果只是对缓变信号进行采样,采样频率比100Hz稍大即可。但是随着采样频率的降低,滤波算法的收敛时间也会增加。因此必须在算法的滤波性能和收敛时间上进行折衷考虑。

本文提出的分配系数法设计数字滤波器,算法速度快、代码效率高、滤波效果理想,是一种实用的数字滤波器设计方法,体现了将算法嵌入到具体硬件的思想。另一方面,将定点小数的表示形式进行适当扩展,这个算法还可以用于10位或16位AD转换精度的应用场合。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码