基于FPGA的IIR数字滤波器的快捷设计

3.2 VHDL代码顶层模块

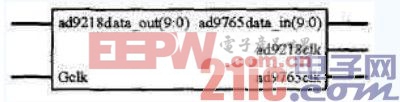

图4是该MATLAB设计的顶层模块“top_lev-el”的示意图。图中,Gclk为FPGA全局时钟输入(来自40MHz晶振),AD9218clk和AD9765clk是由Gclk直通送往AD9218和AD9765的驱动时钟;AD9218data_out(9:0)是来自AD9218的10位滤波器输入信号,设计时可与核心模块“lpf”的输人data_in(9:0)相连;AD9765data_in(9:0)是送往AD9765的10位滤波器输出信号,可与核心模块“lpf”的输出data_out(9:0)相连。

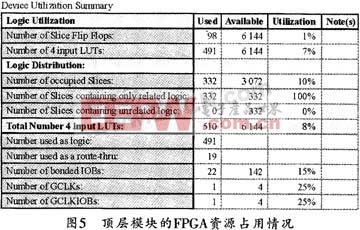

图5给出了顶层模块的FPGA资源占用情况,由图5可见,该系统的资源占用率非常少。

3.3 VHDL代码核心模块

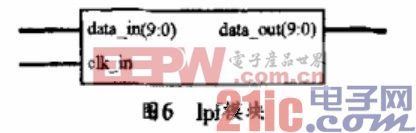

图6所示为用于信号处理的核心模块“lpf”。

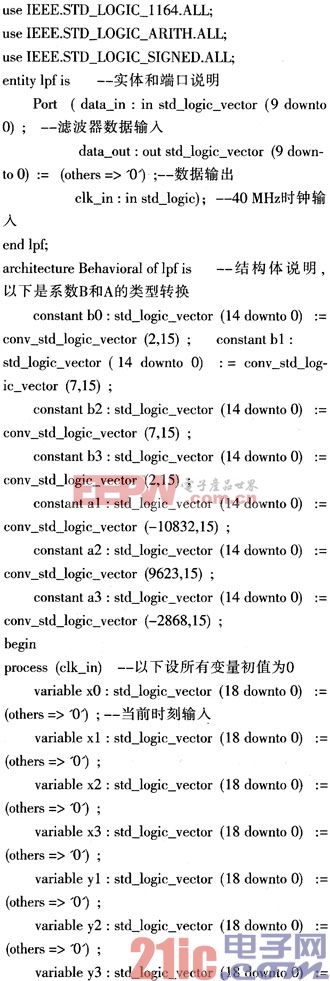

在核心模块VHDL代码编写时应当注意语句“use IEEE.STD_LOGIC_SIGNED.ALL;”,并使用有符号数运算程序包。另外,在将设计好的整数系数B和A转换为二进制补码时,为方便起见,可使用程序包STD_LOGlC_SIGNED.vhd中的类型转换运算符CONV_STD_LOGIC_VECTOR()来接收整数和转换后的长度等两个参数,然后返回STD_LOGIC_VECTOR型。

本系统的代码结构体architecture采用行为描述方式,它类似于高级语言,其优点在于只需描述清楚输入与输出的行为,而无需花费更多的时间和精力关注设计功能的门级实现,因为这些完全可以由EDA工具综合生成,因而可大大缩短开发设计的时间。

核心模块“lpf”的VHDL语言源代码如下:

librarv IEEE;

在modelsim上对本核心模块进行仿真及代码优化时,其测试激励仍然可以分别选用0.5 MHz、3 MHz和6 MHz的正弦波。产生的方法有两种:一是采用ISE中集成的测试激励生成器HDL Bencher新建Test bench waveform型文件,并从中输入一周期正弦数据;二是将正弦数据存为文本文件,然后以TEXTIO方式读取。限于篇幅,具体操作这里不作介绍。

这种行为仿真(Simulate Behavioral Model)的波形与图3相同,可见,本模块源代码在功能上完全正确。但时序仿真(布局布线后仿真SimulatePost-PlaceRoute VHDL Model)的滤波器输出波形中的大幅度尖锐毛刺严重影响了滤波器的性能。消除毛刺的具体做法是将进程中的最后一条信号赋值语句改为:

经过上述赋值语句的修改,再经优化之后进行时序仿真以及后面的硬件验证,就会发现,滤波器输出中的毛刺全部被消除,波形平滑,可见优化效果非常好。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码