基于FPGA和DSP的微振动传感器信号采集系统设计

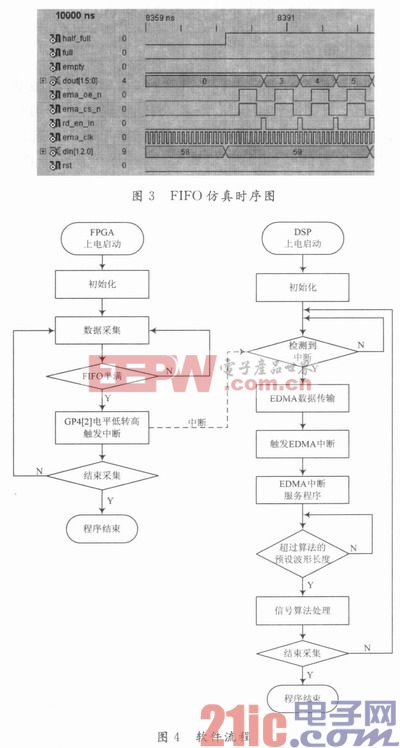

为了避免系统重置之前half_full信号上升沿导致错误的触发DSP的EDMA事件,在rst置位之前half_full置1。模/数转换模块的AD9235输出位数是12位,FIFO的输入和输出均设为12位。

3.2 DSP的软件流程

DSP模块的软件流程设计采用TI的DSP集成开发环境CCS3.3。DSP中的软件配合FPGA上的FIFO一起控制信号的采集和数据的实时处理。软件实现的功能分3个部分:系统初始化,EDMA传输控制和中断服务程序,算法处理。软件流程图如图4所示。

C6747上电后,首先进行系统初始化,设置各配置寄存器使DSP各功能模块按设计要求运行,主要配置管脚复用、PLL、PSC和EMIF。FPGA同时启动并开始控制AD9235开始采集数据,传感器的信号经过模/数转换进入FPGA的FIFO缓冲器,当FIFO内的数据量达到设定长度时,half_ full信号线电平由低转高,输出中断信号。然后,因为此信号线和DSP的通用管脚GP4[2]相连,DSP内部的EDMA3控制器会检测到此GPIO中断事务,并产生一个传输请求,按照设定的参数把数据从FPGA内的输出FIFO转移到DSP模块的SDRAM存储器。在完成此EDMA传输请求之后触发一个EDMA中断,在中断服务程序中检测SDRAM内数据长度。最后,当SDRAM内存储的数据长度达到设定的长度时,触发信号处理函数进行信号处理,譬如对信号进行滤波、小波变换、功率谱分析等。

4 结语

本文基于FPGA和DSP,针对M—Z型光纤微振动传感器设计了一种结构简单、低功耗、实时性能好的信号采集和算法处理的实时系统。测试结果表明系统能采集传感器信号,准确传输到DSP。并进行算法处理;为光纤微振动传感器的数据采集和处理提供了一个良好的解决方案。该系统基于FPGA和DSP,能适应不同的算法,有利于系统的扩展和改进。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码