基于DSP/BIOS的数据采集系统研制

3 多线程机制设计

3.1 DSP/BIOS提供的多线程机制

DSP/BIOS支持的线程按优先级从高到低可以分为硬件中断HWI、软件中断SWI、任务TSK和后台线程IDL。HWI就是ISR,优先级最高,适合200 kHz触发的任务;SWI适合100 ms或者更大周期的触发任务;Task不同SWI之处在于它在执行过程中能被挂起直到必需资源有效,任务之间可以通过queue,semaphore,mailbox进行信息共享;其他线程不运行时才运行IDL;HWI和SWI不能挂起和等待。

3.2 功能划分及任务规划

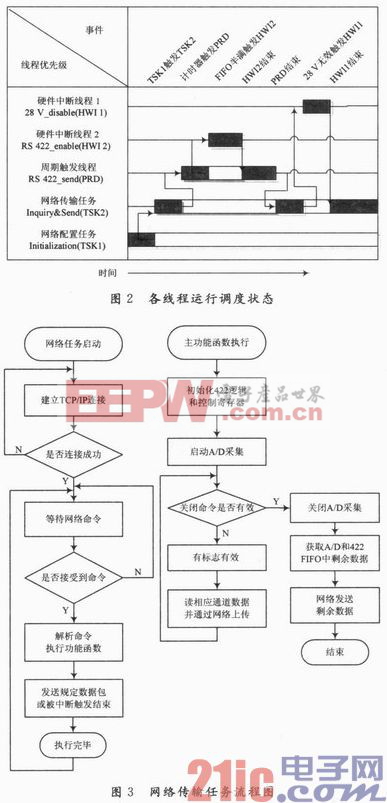

为了优化CPU资源,实现各功能的协调运作,需要合理划分功能、规划任务。本设计中构建了2个硬件中断线程HWI、一个周期触发线程PRD以及网络配置任务线程和网络传输任务线程共5个线程。各线程运行调度状态如图2所示。

3.2.1 硬件中断线程

硬件中断线程主要用来处理响应时间要求严格的请求,同时它的优先级最高,能抢占当前运行的其他线程及时运行。方案中的RS 422通信共5个接收通道,波特率高达614.4 Kb/s,且每个通道的缓冲FIFO只设计了256 B,连续通信时半满触发的时间为2 ms左右。因此,采用HWI处理RS 422通信数据,5个通道共用一个DSP中断源。另外,设计要求被测28 V信号作为AD采集的开关,即28 V有效时启动采集,28 V无效就得中断当前采集任务。因此,通过比较电路将28 V转换为控制信号触发DSP中断。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码