基于FPGA的相关测速系统

(2)Raw to RGB压缩模块

通过内部设置一个1 280×10 bit的FIFO,同时输出两行数据,通过输入的行计数和列计数模块的奇偶将原Byer格式的数据压缩成RGB格式,4个点压缩成一个点,图像大小变成640×512。同时,通过内置的时钟计数模块将当前输出的RGB所在的行列值输出,范围为640×512。

(3)处理流程1

M4K写入控制器:CCD时钟。通过当前输入的行列坐标,确定触发背景M4K内存模块和模板M4K内存模块的写入使能。背景M4K大小设为256×256×4 bit,模板M4K大小设为32×32×4 bit。当该模块工作时,相关模块不工作,以防止未写完数据就做相关处理。

M4K模块:存放处理过的4 bit灰度数据,读写时钟分开,有写使能位。

(4)处理流程2

SdRam接口:提供两个写端口和两个读端口,可同时处理。内部连接了PLL倍频器,将SDRam的处理速度倍增到100 MB,然后通过内部的读写和刷新状态机控制读写。

VGA控制模块:由I2C控制生成行同步信息,并将读入的RGB数据通过系数处理送到解码器输出VGA图像。

测速模块:模板选择的位置固定在图像的正中,即第192行192列开始的32×32大小的数据,通过输入的(X,Y)坐标和(192,192)的差值得到像素的偏移量。然后通过实际的图像大小和距离的比例系数,乘以当前的处理频率,得到当前的物体移动速度。

为了计算偏移量和相对位移,必须引入除法运算,而除法运算是通过许多移位寄存器和加法器构成的。运算极其耗时,且需要大量逻辑单元和查找表,对处理速度有很大影响。所以选取MegaWizard生成的除法器来减少所需的运算时间。

最后,由于实际的数据均为16进制,为了满足显示的10进制坐标换算的需要,设计了16进制到10进制LED显示的转换模块,实现了速度的直观显示,如图3所示。

综上所述,通过模块化设计和综合设计,在FPGA上实现了测速需要的功能设计。

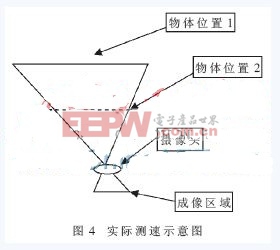

本文对摄像头采集到的数据进行处理。选取图像正中的256×256个像素位置作为背景区域,其中的32×32个像素作为模板选取区域,通过前后两帧的相关得到模板在后一帧中的位移像素值。测速示意图如图4所示。

如果按照理想的相似三角形判断,摄像头可以测量的速度可以达到无限大。设背景区域长宽均为X cm,最大速度可以达到(X×(256-32)/256)/0.529 4=1.9×0.875X cm/s,测量精度为(X/256)/0.529 4=1.9×X/256。但是由于摄像头对光强的敏感程度和目标的实际采样灰度受噪声的影响,以及受安装位置和与被测物体距离的限制,实际测量速度范围是有限的。在测试中采用的背景大小为20 cm×20 cm,离检测面距离30 cm左右,100 MHz工作频率,测速的最大值可达到(20×(256-32)/256)/0.529 4=33.056 cm/s。

整个测速系统可以根据实际应用情况设定参数来调整搜索区域,具有很宽的测速范围。相对于传统的接触式测速系统,克服了物体运动异常时测量出现的原理性误差;相对于非接触的一维测速系统,克服了测速的单一性,可以测量物体在各种运动方向上移动的速度。如果使用高性能FPGA进行多路并行的相关运算,搭配高速高分辨率的摄像头,完全可以解决全图互相关算法处理的计算量巨大的问题,使测速的精度和速度得到进一步提高。这种测速方式具有的一系列优点,使其发展空间非常广阔,可以广泛应用到各个领域。

总之,本文研究的基于FPGA的相关测速系统,能够实现非接触式和高精度的测量。其中,融合了信号采集与处理、逻辑器件FPGA和互相关技术等,具有学科交叉融合的特点。在各种传送带、纸板、热轧钢板、汽车和列车等运动物体的非接触测速上具有较大的实际应用价值,为解决非接触式运动物体测速问题提供了技术手段。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码