TS流的CRC译码器设计

3.4 接收模块

接收模块的主要功能就是检测到起始位后再在每个数据的中央位置进行采样,接收完一帧数据后就放到接收FIFO里供CRC校验模块使用,其RTL视图如图6所示。

4 CRC校验

CRC校验有两种方法:一种是按位来计算的,一种是按字节来计算的。按位来计算的占用FPGA逻辑资源比较少,但是相对来说速度会比较慢,不能适应高速的TS流的要求。按字节来运算的速度快,但是占用FPGA的逻辑资源多。综合考虑后,这里使用按字节的算法。

本设计的CRC算法采用直驱动表法,由于一个字节只有8 b,与生成项进行异或后最多有256个结果,先将256个待查表的值生成MIF文件,放入由FPGA的IP核生成的ROM里,然后用查表法可以达到很快的运算速度,具有很强的实时性。其具体算法如下:

crc_reg=crctab[crc_reg[31:24]^buffer[7:0]8'hff]^{crc_reg[23:0],8'h0};

图7是用model sire对CRC进行仿真的结果使用的是PSI表里的一个section的数据,可以看到,校验到最后的时候,crc_reg的值变为了0,说明数据是正确的。

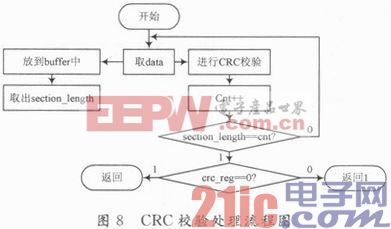

只要在接收FIFO里有数据,CRC模块就会将读取数据进行CRC校验。而每个PSI表里都有一个section_length是记录在这个表里面从该字节之后有多个字节是有效数据的。所以,要将这个数据提取出来再加上3就得到了整个表的长度。在CRC校验的时候,也要设置一个计数器,用于记录处理多少个数据,并与section_length比较。若这两个数相同,则判断CRC寄存器里的值;若为0,则说明这个数据段是正确的,通过串口发0x00给上位机;若CRC寄存器不为0,则说明这个数据断是错误的,FPGA发送0x01给上位机。

CRC校验处理的流程图如图8所示。

5 结论

本系统经过实际验证具有很高的准确性和实时性,并且在上位机和FPGA上都进行了校验,可以验证是否数据在串口传输的过程发生了错误,其FPGA部分可以当作一个独立的模块加入到其他系统中,具有很强的实时性。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码